概述

——

什麼是makefile?或許很多Winodws的程序員都不知道這個東西,因為那些 Windows的IDE都為你做了這個工作,但我覺得要作一個好的和professional的程序員,makefile還是要懂。這就好像現在有這麼多的HTML的編輯器,但如果你想成為一個專業人士,你還是要了解HTML的標識的含義。特別在Unix下的軟體編譯,你就不能不自己寫makefile 了,會不會寫makefile,從一個側面說明了一個人是否具備完成大型專案的能力。

因為,makefile關係到了整個專案的編譯規則。一個專案中的原始碼檔案不計數,其按類型、功能、分別放在若干個目錄中,makefile定義了一系列的規則來指定,哪些檔案需要先編譯,哪些檔案需要後編譯,哪些檔案需要重新編譯,甚至於進行更複雜的功能操作,因為makefile就像一個Shell腳本一樣,其中也可以執行作業系統的命令。

makefile帶來的好處就是——「自動化編譯」,一旦寫好,只需要一個make命令,整個專案完全自動編譯,極大的提高了軟體開發的效率。make是一個命令工具,是一個解釋makefile中指令的命令工具,一般來說,大多數的IDE都有這個命令,比如:Delphi的make,Visual C++的nmake,Linux下GNU的make。可見,makefile都成為了一種在專案方面的編譯方法。

現在講述如何寫makefile的文章比較少,這是我想寫這篇文章的原因。當然,不同產商的 make各不相同,也有不同的語法,但其本質都是在「檔案依賴性」上做文章,這裡,我僅對GNU的make進行講述,我的環境是RedHat Linux 8.0,make的版本是3.80。必竟,這個make是應用最為廣泛的,也是用得最多的。而且其還是最遵循於IEEE 1003.2-1992 標準的(POSIX.2)。

在這篇文檔中,將以C/C++的源碼作為我們基礎,所以必然涉及一些關於C/C++的編譯的知識,相關於這方面的內容,還請各位查看相關的編譯器的文檔。這裡所預設的編譯器是UNIX下的GCC和CC。

關於程序的編譯和連結

——————————

在此,我想多說關於程序編譯的一些規範和方法,一般來說,無論是C、C++、還是pas,首先要把原始碼檔案編譯成中間程式碼檔案,在Windows下也就是 .obj 檔案,UNIX下是 .o 檔案,即 Object File,這個動作叫做編譯(compile)。然後再把大量的Object File合成執行檔案,這個動作叫作連結(link)。

編譯時,編譯器需要的是語法的正確,函數與變量的宣告的正確。對於後者,通常是你需要告訴編譯器頭檔案的所在位置(頭檔案中應該只是宣告,而定義應該放在C/C++檔案中),只要所有的語法正確,編譯器就可以編譯出中間目標檔案。一般來說,每個原始碼檔案都應該對應於一個中間目標檔案(O檔案或是OBJ檔案)。

連結時,主要是連結函數和全域變量,所以,我們可以使用這些中間目標檔案(O檔案或是OBJ檔案)來連結我們的應用程序。連結器並不管函數所在的原始碼檔案,只管函數的中間目標檔案(Object File),在大多數時候,由於原始碼檔案太多,編譯生成的中間目標檔案太多,而在連結時需要明顯地指出中間目標檔案名,這對於編譯很不方便,所以,我們要給中間目標檔案整理成套件,在Windows下這種套件叫「函式庫檔案」(Library File),也就是 .lib 檔案,在UNIX下,是Archive File,也就是 .a 檔案。

總結一下,原始碼檔案首先會生成中間目標檔案,再由中間目標檔案生成執行檔案。在編譯時,編譯器只檢測程序語法,和函數、變量是否被宣告。如果函數未被宣告,編譯器會給出一個警告,但可以生成Object File。而在連結程式時,連結器會在所有的Object File中找尋函數的實現,如果找不到,那到就會報連結錯誤碼(Linker Error),在VC下,這種錯誤一般是:Link 2001錯誤,意思說是說,連結器未能找到函數的實現。你需要指定函數的Object File.

好,言歸正傳,GNU的make有許多的內容,閒言少敘,還是讓我們開始吧。

Makefile 介紹

———————

make命令執行時,需要一個 Makefile 檔案,以告訴make命令需要怎麼樣的去編譯和連結程式。

首先,我們用一個範例來說明Makefile的書寫規則。以便給大家一個感興認識。這個範例來源於GNU的make使用手冊,在這個範例中,我們的專案有8個C檔案,和3個頭檔案,我們要寫一個Makefile來告訴make命令如何編譯和連結這幾個檔案。我們的規則是:

1)如果這個專案沒有編譯過,那麼我們的所有C檔案都要編譯並被連結。

2)如果這個專案的某幾個C檔案被修改,那麼我們只編譯被修改的C檔案,並連結目標程序。

3)如果這個專案的頭檔案被改變了,那麼我們需要編譯引用了這幾個頭檔案的C檔案,並連結目標程序。

只要我們的Makefile寫得夠好,所有的這一切,我們只用一個make命令就可以完成,make命令會自動智能地根據當前的檔案修改的情況來確定哪些檔案需要重編譯,從而自己編譯所需要的檔案和連結目標程序。

一、Makefile的規則

在講述這個Makefile之前,還是讓我們先來粗略地看一看Makefile的規則。

target ... : prerequisites ...

command

...

...

target也就是一個目標檔案,可以是Object File,也可以是執行檔案。還可以是一個標籤(Label),對於標籤這種特性,在後續的「偽目標」章節中會有敘述。

prerequisites就是,要生成那個target所需要的檔案或是目標。

command也就是make需要執行的命令。(任意的Shell命令)

這是一個檔案的依賴關係,也就是說,target這一個或多個的目標檔案依賴於 prerequisites中的檔案,其生成規則定義在command中。說白一點就是說,prerequisites中如果有一個以上的檔案比 target檔案要新的話,command所定義的命令就會被執行。這就是Makefile的規則。也就是Makefile中最核心的內容。

說到底,Makefile的東西就是這樣一點,好像我的這篇文檔也該結束了。呵呵。還不盡然,這是Makefile的主線和核心,但要寫好一個Makefile還不夠,我會以後面一點一點地結合我的工作經驗給你慢慢到來。內容還多著呢。:)

二、一個範例

正如前面所說的,如果一個專案有3個頭檔案,和8個C檔案,我們為了完成前面所述的那三個規則,我們的Makefile應該是下面的這個樣子的。

edit : main.o kbd.o command.o display.o \

insert.o search.o files.o utils.o

cc -o edit main.o kbd.o command.o display.o \

insert.o search.o files.o utils.o

main.o : main.c defs.h

cc -c main.c

kbd.o : kbd.c defs.h command.h

cc -c kbd.c

command.o : command.c defs.h command.h

cc -c command.c

display.o : display.c defs.h buffer.h

cc -c display.c

insert.o : insert.c defs.h buffer.h

cc -c insert.c

search.o : search.c defs.h buffer.h

cc -c search.c

files.o : files.c defs.h buffer.h command.h

cc -c files.c

utils.o : utils.c defs.h

cc -c utils.c

clean :

rm edit main.o kbd.o command.o display.o \

insert.o search.o files.o utils.o

反斜線(\)是換行符的意思。這樣比較便於Makefile的易讀。我們可以把這個內容保存在檔案為「Makefile」或「makefile」的檔案中,然後在該目錄下直接輸入命令「make」就可以生成執行檔案edit。如果要刪除執行檔案和所有的中間目標檔案,那麼,只要簡單地執行一下「make clean」就可以了。

在這個makefile中,目標檔案(target)包含:執行檔案edit和中間目標檔案(*.o),相依性檔案(prerequisites)就是冒號後面的那些 .c 檔案和 .h檔案。每一個 .o 檔案都有一組相依性檔案,而這些 .o 檔案又是執行檔案 edit 的相依性檔案。依賴關係的實質上就是說明了目標檔案是由哪些檔案生成的,換言之,目標檔案是哪些檔案更新的。

在定義好依賴關係後,後續的那一行定義了如何生成目標檔案的作業系統命令,一定要以一個Tab 鍵作為開頭。記住,make並不管命令是怎麼工作的,他只管執行所定義的命令。make會比較targets檔案和prerequisites檔案的修改日期,如果prerequisites檔案的日期要比targets檔案的日期要新,或者target不存在的話,那麼,make就會執行後續定義的命令。

這裡要說明一點的是,clean不是一個檔案,它只不過是一個動作名字,有點像C語言中的 lable一樣,其冒號後什麼也沒有,那麼,make就不會自動去找檔案的依賴性,也就不會自動執行其後所定義的命令。要執行其後的命令,就要在make 命令後明顯得指出這個lable的名字。這樣的方法非常有用,我們可以在一個makefile中定義不用的編譯或是和編譯無關的命令,比如程序的打包,程序的備份,等等。

三、make是如何工作的

在預設的方式下,也就是我們只輸入make命令。那麼,

1、make會在當前目錄下找名字叫「Makefile」或「makefile」的檔案。

2、如果找到,它會找檔案中的第一個目標檔案(target),在上面的例子中,他會找到「edit」這個檔案,並把這個檔案作為最終的目標檔案。

3、如果edit檔案不存在,或是edit所依賴的後面的 .o 檔案的檔案修改時間要比edit這個檔案新,那麼,他就會執行後面所定義的命令來生成edit這個檔案。

4、如果edit所依賴的.o檔案也存在,那麼make會在當前檔案中找目標為.o檔案的依賴性,如果找到則再根據那一個規則生成.o檔案。(這有點像一個堆棧的過程)

5、當然,你的C檔案和H檔案是存在的啦,於是make會生成 .o 檔案,然後再用 .o 檔案生命make的終極任務,也就是執行檔案edit了。

這就是整個make的依賴性,make會一層又一層地去找檔案的依賴關係,直到最終編譯出第一個目標檔案。在找尋的過程中,如果出現錯誤,比如最後被依賴的檔案找不到,那麼make就會直接退出,並報錯,而對於所定義的命令的錯誤,或是編譯不成功,make根本不理。make只管檔案的依賴性,即,如果在我找了依賴關係之後,冒號後面的檔案還是不在,那麼對不起,我就不工作啦。

通過上述分析,我們知道,像clean這種,沒有被第一個目標檔案直接或間接關聯,那麼它後面所定義的命令將不會被自動執行,不過,我們可以顯示要make執行。即命令——「make clean」,以此來清除所有的目標檔案,以便重編譯。

於是在我們編程中,如果這個專案已被編譯過了,當我們修改了其中一個原始碼檔案,比如 file.c,那麼根據我們的依賴性,我們的目標file.o會被重編譯(也就是在這個依性關係後面所定義的命令),於是file.o的檔案也是最新的啦,於是file.o的檔案修改時間要比edit要新,所以edit也會被重新連結了(詳見edit目標檔案後定義的命令)。

而如果我們改變了「command.h」,那麼,kdb.o、command.o和files.o都會被重編譯,並且,edit會被重連結。

四、makefile中使用變量

在上面的例子中,先讓我們看看edit的規則:

edit : main.o kbd.o command.o display.o \

insert.o search.o files.o utils.o

cc -o edit main.o kbd.o command.o display.o \

insert.o search.o files.o utils.o

我們可以看到[.o]檔案的字串被重複了兩次,如果我們的專案需要加入一個新的[.o]檔案,那麼我們需要在兩個地方加(應該是三個地方,還有一個地方在clean中)。當然,我們的makefile並不複雜,所以在兩個地方加也不累,但如果 makefile變得複雜,那麼我們就有可能會忘掉一個需要加入的地方,而導致編譯失敗。所以,為了makefile的易維護,在makefile中我們可以使用變量。makefile的變量也就是一個字串,理解成C語言中的宏可能會更好。

比如,我們宣告一個變量,叫objects, OBJECTS, objs, OBJS, obj, 或是 OBJ,反正不管什麼啦,只要能夠表示obj檔案就行了。我們在makefile一開始就這樣定義:

objects = main.o kbd.o command.o display.o \

insert.o search.o files.o utils.o

於是,我們就可以很方便地在我們的makefile中以「$(objects)」的方式來使用這個變量了,於是我們的改良版makefile就變成下面這個樣子:

objects = main.o kbd.o command.o display.o \

insert.o search.o files.o utils.o

edit : $(objects)

cc -o edit $(objects)

main.o : main.c defs.h

cc -c main.c

kbd.o : kbd.c defs.h command.h

cc -c kbd.c

command.o : command.c defs.h command.h

cc -c command.c

display.o : display.c defs.h buffer.h

cc -c display.c

insert.o : insert.c defs.h buffer.h

cc -c insert.c

search.o : search.c defs.h buffer.h

cc -c search.c

files.o : files.c defs.h buffer.h command.h

cc -c files.c

utils.o : utils.c defs.h

cc -c utils.c

clean :

rm edit $(objects)

於是如果有新的 .o 檔案加入,我們只需簡單地修改一下 objects 變量就可以了。

關於變量更多的話題,我會在後續給你一一道來。

五、讓make自動推導

GNU的make很強大,它可以自動推導檔案以及檔案依賴關係後面的命令,於是我們就沒必要去在每一個[.o]檔案後都寫上類似的命令,因為,我們的make會自動識別,並自己推導命令。

只要make看到一個[.o]檔案,它就會自動的把[.c]檔案加在依賴關係中,如果make 找到一個whatever.o,那麼whatever.c,就會是whatever.o的相依性檔案。並且 cc -c whatever.c 也會被推導出來,於是,我們的makefile再也不用寫得這麼複雜。我們的是新的makefile又出爐了。

objects = main.o kbd.o command.o display.o \

insert.o search.o files.o utils.o

edit : $(objects)

cc -o edit $(objects)

main.o : defs.h

kbd.o : defs.h command.h

command.o : defs.h command.h

display.o : defs.h buffer.h

insert.o : defs.h buffer.h

search.o : defs.h buffer.h

files.o : defs.h buffer.h command.h

utils.o : defs.h

.PHONY : clean

clean :

rm edit $(objects)

這種方法,也就是make的「隱晦規則」。上面檔案內容中,「.PHONY」表示,clean是個偽目標檔案。

關於更為詳細的「隱晦規則」和「偽目標檔案」,我會在後續給你一一道來。

六、另類風格的makefile

即然我們的make可以自動推導命令,那麼我看到那堆[.o]和[.h]的依賴就有點不爽,那麼多的重複的[.h],能不能把其收攏起來,好吧,沒有問題,這個對於make來說很容易,誰叫它提供了自動推導命令和檔案的功能呢?來看看最新風格的makefile吧。

objects = main.o kbd.o command.o display.o \

insert.o search.o files.o utils.o

edit : $(objects)

cc -o edit $(objects)

$(objects) : defs.h

kbd.o command.o files.o : command.h

display.o insert.o search.o files.o : buffer.h

.PHONY : clean

clean :

rm edit $(objects)

這種風格,讓我們的makefile變得很簡單,但我們的檔案依賴關係就顯得有點凌亂了。魚和熊掌不可兼得。還看你的喜好了。我是不喜歡這種風格的,一是檔案的依賴關係看不清楚,二是如果檔案一多,要加入幾個新的.o檔案,那就理不清楚了。

七、清空目標檔案的規則

每個Makefile中都應該寫一個清空目標檔案(.o和執行檔案)的規則,這不僅便於重編譯,也很利於保持檔案的清潔。這是一個「修養」(呵呵,還記得我的《編程修養》嗎)。一般的風格都是:

clean:

rm edit $(objects)

更為穩健的做法是:

.PHONY : clean

clean :

-rm edit $(objects)

前面說過,.PHONY意思表示clean是一個「偽目標」,。而在rm命令前面加了一個小減號的意思就是,也許某些檔案出現問題,但不要管,繼續做後面的事。當然,clean的規則不要放在檔案的開頭,不然,這就會變成make的預設目標,相信誰也不願意這樣。不成文的規矩是——「clean從來都是放在檔案的最後」。

上面就是一個makefile的概貌,也是makefile的基礎,下面還有很多makefile的相關細節,準備好了嗎?準備好了就來。

Makefile 總述

———————

一、Makefile裡有什麼?

Makefile裡主要包含了五個東西:顯式規則、隱晦規則、變量定義、檔案指示和註釋。

1、顯式規則。顯式規則說明了,如何生成一個或多的的目標檔案。這是由Makefile的書寫者明顯指出,要生成的檔案,檔案的相依性檔案,生成的命令。

2、隱晦規則。由於我們的make有自動推導的功能,所以隱晦的規則可以讓我們比較粗糙地簡略地書寫Makefile,這是由make所支持的。

3、變量的定義。在Makefile中我們要定義一系列的變量,變量一般都是字串,這個有點你C語言中的宏,當Makefile被執行時,其中的變量都會被擴展到相應的引用位置上。

4、檔案指示。其包括了三個部分,一個是在一個Makefile中引用另一個 Makefile,就像C語言中的include一樣;另一個是指根據某些情況指定Makefile中的有效部分,就像C語言中的預編譯#if一樣;還有就是定義一個多行的命令。有關這一部分的內容,我會在後續的部分中講述。

5、註釋。Makefile中只有行註釋,和UNIX的Shell腳本一樣,其註釋是用「#」字符,這個就像C/C++中的「//」一樣。如果你要在你的Makefile中使用「#」字符,可以用反斜框進行轉義,如:「\#」。

最後,還值得一提的是,在Makefile中的命令,必須要以[Tab]鍵開始。

二、Makefile的檔案名

預設的情況下,make命令會在當前目錄下按順序找尋檔案名為「GNUmakefile」、「makefile」、「Makefile」的檔案,找到了解釋這個檔案。在這三個檔案名中,最好使用「Makefile」這個檔案名,因為,這個檔案名第一個字符為大寫,這樣有一種顯目的感覺。最好不要用「GNUmakefile」,這個檔案是GNU的make識別的。有另外一些make只對全小寫的「makefile」檔案名敏感,但是基本上來說,大多數的make都支持「makefile」和「Makefile」這兩種預設檔案名。

當然,你可以使用別的檔案名來書寫Makefile,比如:「Make.Linux」,「Make.Solaris」,「Make.AIX」等,如果要指定特定的Makefile,你可以使用make的「-f」和「--file」參數,如: make -f Make.Linux或make --file Make.AIX。

三、引用其它的Makefile

在Makefile使用include關鍵字可以把別的Makefile包含進來,這很像C語言的#include,被包含的檔案會原模原樣的放在當前檔案的包含位置。include的語法是:

include <filename>

filename可以是當前作業系統Shell的檔案模式(可以保含路徑和通配符)

在include前面可以有一些空字符,但是絕不能是[Tab]鍵開始。include和 <filename>可以用一個或多個空格隔開。舉個例子,你有這樣幾個Makefile:a.mk、b.mk、c.mk,還有一個檔案叫 foo.make,以及一個變量$(bar),其包含了e.mk和f.mk,那麼,下面的語句:

include foo.make *.mk $(bar)

等價於:

include foo.make a.mk b.mk c.mk e.mk f.mk

make命令開始時,會把找尋include所指出的其它Makefile,並把其內容安置在當前的位置。就好像C/C++的#include指令一樣。如果檔案都沒有指定絕對路徑或是相對路徑的話,make會在當前目錄下首先尋找,如果當前目錄下沒有找到,那麼,make還會在下面的幾個目錄下找:

1、如果make執行時,有「-I」或「--include-dir」參數,那麼make就會在這個參數所指定的目錄下去尋找。

2、如果目錄<prefix>/include(一般是:/usr/local/bin或/usr/include)存在的話,make也會去找。

如果有檔案沒有找到的話,make會生成一條警告訊息,但不會馬上出現致命錯誤。它會繼續載入其它的檔案,一旦完成makefile的讀取,make會再重試這些沒有找到,或是不能讀取的檔案,如果還是不行,make才會出現一條致命訊息。如果你想讓make不理那些無法讀取的檔案,而繼續執行,你可以在include前加一個減號「-」。如:

-include <filename>

其表示,無論include過程中出現什麼錯誤,都不要報錯繼續執行。和其它版本make兼容的相關命令是sinclude,其作用和這一個是一樣的。

四、環境變量 MAKEFILES

如果你的當前環境中定義了環境變量MAKEFILES,那麼,make會把這個變量中的值做一個類似於include的動作。這個變量中的值是其它的Makefile,用空格分隔。只是,它和include不同的是,從這個環境變中引入的 Makefile的「目標」不會起作用,如果環境變量中定義的檔案發現錯誤,make也會不理。

但是在這裡我還是建議不要使用這個環境變量,因為只要這個變量一被定義,那麼當你使用make 時,所有的Makefile都會受到它的影響,這絕不是你想看到的。在這裡提這個事,只是為了告訴大家,也許有時候你的Makefile出現了怪事,那麼你可以看看當前環境中有沒有定義這個變量。

五、make的工作方式

GNU的make工作時的執行步驟入下:(想來其它的make也是類似)

1、讀入所有的Makefile。

2、讀入被include的其它Makefile。

3、初始化檔案中的變量。

4、推導隱晦規則,並分析所有規則。

5、為所有的目標檔案建立依賴關係鏈。

6、根據依賴關係,決定哪些目標要重新生成。

7、執行生成命令。

1-5步為第一個階段,6-7為第二個階段。第一個階段中,如果定義的變量被使用了,那麼, make會把其展開在使用的位置。但make並不會完全馬上展開,make使用的是拖延戰術,如果變量出現在依賴關係的規則中,那麼僅當這條依賴被決定要使用了,變量才會在其內部展開。

當然,這個工作方式你不一定要清楚,但是知道這個方式你也會對make更為熟悉。有了這個基礎,後續部分也就容易看懂了。

書寫規則

————

規則包含兩個部分,一個是依賴關係,一個是生成目標的方法。

在Makefile中,規則的順序是很重要的,因為,Makefile中只應該有一個最終目標,其它的目標都是被這個目標所連帶出來的,所以一定要讓make知道你的最終目標是什麼。一般來說,定義在Makefile中的目標可能會有很多,但是第一條規則中的目標將被確立為最終的目標。如果第一條規則中的目標有很多個,那麼,第一個目標會成為最終的目標。make所完成的也就是這個目標。

好了,還是讓我們來看一看如何書寫規則。

一、規則舉例

foo.o : foo.c defs.h # foo模組

cc -c -g foo.c

看到這個例子,各位應該不是很陌生了,前面也已說過,foo.o是我們的目標,foo.c和defs.h是目標所依賴的原始碼檔案,而只有一個命令「cc -c -g foo.c」(以Tab鍵開頭)。這個規則告訴我們兩件事:

1、檔案的依賴關係,foo.o依賴於foo.c和defs.h的檔案,如果foo.c和defs.h的檔案日期要比foo.o檔案日期要新,或是foo.o不存在,那麼依賴關係發生。

2、如果生成(或更新)foo.o檔案。也就是那個cc命令,其說明了,如何生成foo.o這個檔案。(當然foo.c檔案include了defs.h檔案)

二、規則的語法

targets : prerequisites

command

...

或是這樣:

targets : prerequisites ; command

command

...

targets是檔案名,以空格分開,可以使用通配符。一般來說,我們的目標基本上是一個檔案,但也有可能是多個檔案。

command是命令行,如果其不與「target:prerequisites」在一行,那麼,必須以[Tab鍵]開頭,如果和prerequisites在一行,那麼可以用分號做為分隔。(見上)

prerequisites也就是目標所依賴的檔案(或依賴目標)。如果其中的某個檔案要比目標檔案要新,那麼,目標就被認為是「過時的」,被認為是需要重生成的。這個在前面已經講過了。

如果命令太長,你可以使用反斜框(『\')作為換行符。make對一行上有多少個字符沒有限制。規則告訴make兩件事,檔案的依賴關係和如何成成目標檔案。

一般來說,make會以UNIX的標準Shell,也就是/bin/sh來執行命令。

三、在規則中使用通配符

如果我們想定義一系列比較類似的檔案,我們很自然地就想起使用通配符。make支持三各通配符:「*」,「?」和「[...]」。這是和Unix的B-Shell是相同的。

波浪號(「~」)字符在檔案名中也有比較特殊的用途。如果是「~/test」,這就表示當前用戶的$HOME目錄下的test目錄。而「~hchen/test」則表示用戶hchen的宿主目錄下的test目錄。(這些都是Unix下的小知識了, make也支持)而在Windows或是MS-DOS下,用戶沒有宿主目錄,那麼波浪號所指的目錄則根據環境變量「HOME」而定。

通配符代替了你一系列的檔案,如「*.c」表示所以後綴為c的檔案。一個需要我們注意的是,如果我們的檔案名中有通配符,如:「*」,那麼可以用轉義字符「\」,如「\*」來表示真實的「*」字符,而不是任意長度的字串。

好吧,還是先來看幾個例子吧:

clean:

rm -f *.o

上面這個例子我不不多說了,這是作業系統Shell所支持的通配符。這是在命令中的通配符。

print: *.c

lpr -p $?

touch print

上面這個例子說明了通配符也可以在我們的規則中,目標print依賴於所有的[.c]檔案。其中的「$?」是一個自動化變量,我會在後面給你講述。

objects = *.o

上面這個例子,表示了,通符同樣可以用在變量中。並不是說[*.o]會展開,不!objects的值就是「*.o」。Makefile中的變量其實就是 C/C++中的宏。如果你要讓通配符在變量中展開,也就是讓objects的值是所有[.o]的檔案名的集合,那麼,你可以這樣:

objects := $(wildcard *.o)

這種用法由關鍵字「wildcard」指出,關於Makefile的關鍵字,我們將在後面討論。

四、檔案搜尋

在一些大的專案中,有大量的原始碼檔案,我們通常的做法是把這許多的原始碼檔案分類,並存放在不同的目錄中。所以,當make需要去找尋檔案的依賴關係時,你可以在檔案前加上路徑,但最好的方法是把一個路徑告訴make,讓make在自動去找。

Makefile檔案中的特殊變量「VPATH」就是完成這個功能的,如果沒有指明這個變量,make只會在當前的目錄中去找尋相依性檔案和目標檔案。如果定義了這個變量,那麼,make就會在噹噹前目錄找不到的情況下,到所指定的目錄中去找尋檔案了。

VPATH = src:../headers

上面的的定義指定兩個目錄,「src」和「../headers」,make會按照這個順序進行搜索。目錄由「冒號」分隔。(當然,當前目錄永遠是最高優先搜索的地方)

另一個設置檔案搜索路徑的方法是使用make的「vpath」關鍵字(注意,它是全小寫的),這不是變量,這是一個make的關鍵字,這和上面提到的那個VPATH變量很類似,但是它更為靈活。它可以指定不同的檔案在不同的搜索目錄中。這是一個很靈活的功能。它的使用方法有三種:

1、vpath <pattern> <directories>

為符合模式<pattern>的檔案指定搜索目錄<directories>。

2、vpath <pattern>

清除符合模式<pattern>的檔案的搜索目錄。

3、vpath

清除所有已被設置好了的檔案搜索目錄。

vapth使用方法中的<pattern>需要包含「%」字符。「%」的意思是匹配零或若干字符,例如,「%.h」表示所有以「.h」結尾的檔案。<pattern>指定了要搜索的檔案集,而< directories>則指定了<pattern>的檔案集的搜索的目錄。例如:

vpath %.h ../headers

該語句表示,要求make在「../headers」目錄下搜索所有以「.h」結尾的檔案。(如果某檔案在當前目錄沒有找到的話)

我們可以連續地使用vpath語句,以指定不同搜索策略。如果連續的vpath語句中出現了相同的<pattern>,或是被重複了的<pattern>,那麼,make會按照vpath語句的先後順序來執行搜索。如:

vpath %.c foo

vpath % blish

vpath %.c bar

其表示「.c」結尾的檔案,先在「foo」目錄,然後是「blish」,最後是「bar」目錄。

vpath %.c foo:bar

vpath % blish

而上面的語句則表示「.c」結尾的檔案,先在「foo」目錄,然後是「bar」目錄,最後才是「blish」目錄。

五、偽目標

最早先的一個例子中,我們提到過一個「clean」的目標,這是一個「偽目標」,

clean:

rm *.o temp

正像我們前面例子中的「clean」一樣,即然我們生成了許多檔案編譯檔案,我們也應該提供一個清除它們的「目標」以備完整地重編譯而用。 (以「make clean」來使用該目標)

因為,我們並不生成「clean」這個檔案。「偽目標」並不是一個檔案,只是一個標籤,由於「偽目標」不是檔案,所以make無法生成它的依賴關係和決定它是否要執行。我們只有通過顯示地指明這個「目標」才能讓其生效。當然,「偽目標」的取名不能和檔案名重名,不然其就失去了「偽目標」的意義了。

當然,為了避免和檔案重名的這種情況,我們可以使用一個特殊的標記「.PHONY」來顯示地指明一個目標是「偽目標」,向make說明,不管是否有這個檔案,這個目標就是「偽目標」。

.PHONY : clean

只要有這個宣告,不管是否有「clean」檔案,要運行「clean」這個目標,只有「make clean」這樣。於是整個過程可以這樣寫:

.PHONY: clean

clean:

rm *.o temp

偽目標一般沒有依賴的檔案。但是,我們也可以為偽目標指定所依賴的檔案。偽目標同樣可以作為「預設目標」,只要將其放在第一個。一個範例就是,如果你的Makefile需要一口氣生成若干個可執行檔案,但你只想簡單地敲一個make完事,並且,所有的目標檔案都寫在一個Makefile中,那麼你可以使用「偽目標」這個特性:

all : prog1 prog2 prog3

.PHONY : all

prog1 : prog1.o utils.o

cc -o prog1 prog1.o utils.o

prog2 : prog2.o

cc -o prog2 prog2.o

prog3 : prog3.o sort.o utils.o

cc -o prog3 prog3.o sort.o utils.o

我們知道,Makefile中的第一個目標會被作為其預設目標。我們宣告了一個「all」的偽目標,其依賴於其它三個目標。由於偽目標的特性是,總是被執行的,所以其依賴的那三個目標就總是不如「all」這個目標新。所以,其它三個目標的規則總是會被決議。也就達到了我們一口氣生成多個目標的目的。「.PHONY : all」宣告了「all」這個目標為「偽目標」。

隨便提一句,從上面的例子我們可以看出,目標也可以成為依賴。所以,偽目標同樣也可成為依賴。看下面的例子:

.PHONY: cleanall cleanobj cleandiff

cleanall : cleanobj cleandiff

rm program

cleanobj :

rm *.o

cleandiff :

rm *.diff

「make clean」將清除所有要被清除的檔案。「cleanobj」和「cleandiff」這兩個偽目標有點像「子程序」的意思。我們可以輸入「make cleanall」和「make cleanobj」和「make cleandiff」命令來達到清除不同種類檔案的目的。

六、多目標

Makefile的規則中的目標可以不止一個,其支持多目標,有可能我們的多個目標同時依賴於一個檔案,並且其生成的命令大體類似。於是我們就能把其合併起來。當然,多個目標的生成規則的執行命令是同一個,這可能會可我們帶來麻煩,不過好在我們的可以使用一個自動化變量「$@」(關於自動化變量,將在後面講述),這個變量表示著目前規則中所有的目標的集合,這樣說可能很抽象,還是看一個例子吧。

bigoutput littleoutput : text.g

generate text.g -$(subst output,,$@) > $@

上述規則等價於:

bigoutput : text.g

generate text.g -big > bigoutput

littleoutput : text.g

generate text.g -little > littleoutput

其中,-$(subst output,,$@)中的「$」表示執行一個Makefile的函數,函數名為subst,後面的為參數。關於函數,將在後面講述。這裡的這個函數是截取字串的意思,「$@」表示目標的集合,就像一個數組,「$@」依次取出目標,並執於命令。

七、靜態模式

靜態模式可以更加容易地定義多目標的規則,可以讓我們的規則變得更加的有彈性和靈活。我們還是先來看一下語法:

<targets ...>: <target-pattern>: <prereq-patterns ...>

<commands>

...

targets定義了一系列的目標檔案,可以有通配符。是目標的一個集合。

target-parrtern是指明了targets的模式,也就是的目標集模式。

prereq-parrterns是目標的依賴模式,它對target-parrtern形成的模式再進行一次依賴目標的定義。

這樣描述這三個東西,可能還是沒有說清楚,還是舉個例子來說明一下吧。如果我們的< target-parrtern>定義成「%.o」,意思是我們的<target>集合中都是以「.o」結尾的,而如果我們的< prereq-parrterns>定義成「%.c」,意思是對<target-parrtern>所形成的目標集進行二次定義,其計算方法是,取<target-parrtern>模式中的「%」(也就是去掉了[.o]這個結尾),並為其加上[.c]這個結尾,形成的新集合。

所以,我們的「目標模式」或是「依賴模式」中都應該有「%」這個字符,如果你的檔案名中有「%」那麼你可以使用反斜線「\」進行轉義,來標明真實的「%」字符。

看一個例子:

objects = foo.o bar.o

all: $(objects)

$(objects): %.o: %.c

$(CC) -c $(CFLAGS) $< -o $@

上面的例子中,指明了我們的目標從$object中獲取,「%.o」表明要所有以「.o」結尾的目標,也就是「foo.o bar.o」,也就是變量$object集合的模式,而依賴模式「%.c」則取模式「%.o」的「%」,也就是「foo bar」,並為其加下「.c」的後綴,於是,我們的依賴目標就是「foo.c bar.c」。而命令中的「$<」和「$@」則是自動化變量,「$<」表示所有的依賴目標集(也就是「foo.c bar.c」),「$@」表示目標集(也就是「foo.o bar.o」)。於是,上面的規則展開後等價於下面的規則:

foo.o : foo.c

$(CC) -c $(CFLAGS) foo.c -o foo.o

bar.o : bar.c

$(CC) -c $(CFLAGS) bar.c -o bar.o

試想,如果我們的「%.o」有幾百個,那種我們只要用這種很簡單的「靜態模式規則」就可以寫完一堆規則,實在是太有效率了。「靜態模式規則」的用法很靈活,如果用得好,那會一個很強大的功能。再看一個例子:

files = foo.elc bar.o lose.o

$(filter %.o,$(files)): %.o: %.c

$(CC) -c $(CFLAGS) $< -o $@

$(filter %.elc,$(files)): %.elc: %.el

emacs -f batch-byte-compile $<

$(filter %.o,$(files))表示呼叫Makefile的filter函數,過濾「$filter」集,只要其中模式為「%.o」的內容。其的它內容,我就不用多說了吧。這個例字展示了Makefile中更大的彈性。

八、自動生成依賴性

在Makefile中,我們的依賴關係可能會需要包含一系列的頭檔案,比如,如果我們的main.c中有一句「#include "defs.h"」,那麼我們的依賴關係應該是:

main.o : main.c defs.h

但是,如果是一個比較大型的專案,你必需清楚哪些C檔案包含了哪些頭檔案,並且,你在加入或刪除頭檔案時,也需要小心地修改Makefile,這是一個很沒有維護性的工作。為了避免這種繁重而又容易出錯的事情,我們可以使用C/C++編譯的一個功能。大多數的C/C++編譯器都支持一個「-M」的選項,即自動找尋原始碼檔案中包含的頭檔案,並生成一個依賴關係。例如,如果我們執行下面的命令:

cc -M main.c

其輸出是:

main.o : main.c defs.h

於是由編譯器自動生成的依賴關係,這樣一來,你就不必再手動書寫若干檔案的依賴關係,而由編譯器自動生成了。需要提醒一句的是,如果你使用GNU的C/C++編譯器,你得用「-MM」參數,不然,「-M」參數會把一些標準庫的頭檔案也包含進來。

gcc -M main.c的輸出是:

main.o: main.c defs.h /usr/include/stdio.h /usr/include/features.h \

/usr/include/sys/cdefs.h /usr/include/gnu/stubs.h \

/usr/lib/gcc-lib/i486-suse-linux/2.95.3/include/stddef.h \

/usr/include/bits/types.h /usr/include/bits/pthreadtypes.h \

/usr/include/bits/sched.h /usr/include/libio.h \

/usr/include/_G_config.h /usr/include/wchar.h \

/usr/include/bits/wchar.h /usr/include/gconv.h \

/usr/lib/gcc-lib/i486-suse-linux/2.95.3/include/stdarg.h \

/usr/include/bits/stdio_lim.h

gcc -MM main.c的輸出則是:

main.o: main.c defs.h

那麼,編譯器的這個功能如何與我們的Makefile聯繫在一起呢。因為這樣一來,我們的 Makefile也要根據這些原始碼檔案重新生成,讓Makefile自已依賴於原始碼檔案?這個功能並不現實,不過我們可以有其它手段來迂迴地實現這一功能。 GNU組織建議把編譯器為每一個原始碼檔案的自動生成的依賴關係放到一個檔案中,為每一個「name.c」的檔案都生成一個「name.d」的 Makefile檔案,[.d]檔案中就存放對應[.c]檔案的依賴關係。

於是,我們可以寫出[.c]檔案和[.d]檔案的依賴關係,並讓make自動更新或自成[.d]檔案,並把其包含在我們的主Makefile中,這樣,我們就可以自動化地生成每個檔案的依賴關係了。

這裡,我們給出了一個模式規則來產生[.d]檔案:

%.d: %.c

@set -e; rm -f $@; \

$(CC) -M $(CPPFLAGS) $< > $@.$$$$ ; \

sed 's,\($*\)\.o[ :]*,\1.o $@ : ,g' < $@.$$$$ > $@; \

rm -f $@.$$$$

這個規則的意思是,所有的[.d]檔案依賴於[.c]檔案,「rm -f $@」的意思是刪除所有的目標,也就是[.d]檔案,第二行的意思是,為每個相依性檔案「$<」,也就是[.c]檔案生成相依性檔案,「$@」表示模式「%.d」檔案,如果有一個C檔案是name.c,那麼「%」就是「name」,「$$$$」意為一個隨機編號,第二行生成的檔案有可能是「name.d.12345」,第三行使用sed命令做了一個替換,關於sed命令的用法請參看相關的使用文檔。第四行就是刪除臨時檔案。

總而言之,這個模式要做的事就是在編譯器生成的依賴關係中加入[.d]檔案的依賴,即把依賴關係:

main.o : main.c defs.h

轉成:

main.o main.d : main.c defs.h

於是,我們的[.d]檔案也會自動更新了,並會自動生成了,當然,你還可以在這個[.d]檔案中加入的不只是依賴關係,包括生成的命令也可一併加入,讓每個[.d]檔案都包含一個完賴的規則。一旦我們完成這個工作,接下來,我們就要把這些自動生成的規則放進我們的主Makefile中。我們可以使用Makefile的「include」命令,來引入別的Makefile檔案(前面講過),例如:

sources = foo.c bar.c

include $(sources:.c=.d)

上述語句中的「$(sources:.c=.d)」中的「.c=.d」的意思是做一個替換,把變量$(sources)所有[.c]的字串都替換成[.d],關於這個「替換」的內容,在後面我會有更為詳細的講述。當然,你得注意次序,因為 include是按次來載入檔案,最先載入的[.d]檔案中的目標會成為預設目標。

書寫命令

————

每條規則中的命令和作業系統Shell的命令行是一致的。make會一按順序一條一條的執行命令,每條命令的開頭必須以[Tab]鍵開頭,除非,命令是緊跟在依賴規則後面的分號後的。在命令行之間中的空格或是空行會被忽略,但是如果該空格或空行是以Tab鍵開頭的,那麼make會認為其是一個空命令。

我們在UNIX下可能會使用不同的Shell,但是make的命令預設是被「/bin/sh」——UNIX的標準Shell解釋執行的。除非你特別指定一個其它的Shell。Makefile中,「#」是註釋符,很像C/C++中的「//」,其後的本行字符都被註釋。

一、顯示命令

通常,make會把其要執行的命令行在命令執行前輸出到屏幕上。當我們用「@」字符在命令行前,那麼,這個命令將不被make顯示出來,最具代表性的例子是,我們用這個功能來像屏幕顯示一些訊息。如:

@echo 正在編譯XXX模組......

當make執行時,會輸出「正在編譯XXX模組......」字串,但不會輸出命令,如果沒有「@」,那麼,make將輸出:

echo 正在編譯XXX模組......

正在編譯XXX模組......

如果make執行時,帶入make參數「-n」或「--just-print」,那麼其只是顯示命令,但不會執行命令,這個功能很有利於我們調試我們的Makefile,看看我們書寫的命令是執行起來是什麼樣子的或是什麼順序的。

而make參數「-s」或「--slient」則是全面禁止命令的顯示。

二、命令執行

當依賴目標新於目標時,也就是當規則的目標需要被更新時,make會一條一條的執行其後的命令。需要注意的是,如果你要讓上一條命令的結果應用在下一條命令時,你應該使用分號分隔這兩條命令。比如你的第一條命令是cd命令,你希望第二條命令得在 cd之後的基礎上運行,那麼你就不能把這兩條命令寫在兩行上,而應該把這兩條命令寫在一行上,用分號分隔。如:

範例一:

exec:

cd /home/hchen

pwd

範例二:

exec:

cd /home/hchen; pwd

當我們執行「make exec」時,第一個例子中的cd沒有作用,pwd會打印出當前的Makefile目錄,而第二個例子中,cd就起作用了,pwd會打印出「/home/hchen」。

make一般是使用環境變量SHELL中所定義的系統Shell來執行命令,預設情況下使用 UNIX的標準Shell——/bin/sh來執行命令。但在MS-DOS下有點特殊,因為MS-DOS下沒有SHELL環境變量,當然你也可以指定。如果你指定了UNIX風格的目錄形式,首先,make會在SHELL所指定的路徑中找尋命令解釋器,如果找不到,其會在當前盤符中的當前目錄中尋找,如果再找不到,其會在PATH環境變量中所定義的所有路徑中尋找。MS-DOS中,如果你定義的命令解釋器沒有找到,其會給你的命令解釋器加上諸如「.exe」、「.com」、「.bat」、「.sh」等後綴。

三、命令出錯

每當命令運行完後,make會檢測每個命令的返回碼,如果命令返回成功,那麼make會執行下一條命令,當規則中所有的命令成功返回後,這個規則就算是成功完成了。如果一個規則中的某個命令出錯了(命令退出碼非零),那麼make就會終止執行當前規則,這將有可能終止所有規則的執行。

有些時候,命令的出錯並不表示就是錯誤的。例如mkdir命令,我們一定需要建立一個目錄,如果目錄不存在,那麼mkdir就成功執行,萬事大吉,如果目錄存在,那麼就出錯了。我們之所以使用mkdir的意思就是一定要有這樣的一個目錄,於是我們就不希望mkdir出錯而終止規則的運行。

為了做到這一點,忽略命令的出錯,我們可以在Makefile的命令行前加一個減號「-」(在Tab鍵之後),標記為不管命令出不出錯都認為是成功的。如:

clean:

-rm -f *.o

還有一個全域的辦法是,給make加上「-i」或是「--ignore-errors」參數,那麼,Makefile中所有命令都會忽略錯誤。而如果一個規則是以「.IGNORE」作為目標的,那麼這個規則中的所有命令將會忽略錯誤。這些是不同級別的防止命令出錯的方法,你可以根據你的不同喜歡設置。

還有一個要提一下的make的參數的是「-k」或是「--keep-going」,這個參數的意思是,如果某規則中的命令出錯了,那麼就終目該規則的執行,但繼續執行其它規則。

四、巢狀執行make

在一些大的專案中,我們會把我們不同模組或是不同功能的原始碼檔案放在不同的目錄中,我們可以在每個目錄中都書寫一個該目錄的Makefile,這有利於讓我們的Makefile變得更加地簡潔,而不至於把所有的東西全部寫在一個Makefile中,這樣會很難維護我們的Makefile,這個技術對於我們模組編譯和分段編譯有著非常大的好處。

例如,我們有一個子目錄叫subdir,這個目錄下有個Makefile檔案,來指明了這個目錄下檔案的編譯規則。那麼我們總控的Makefile可以這樣書寫:

subsystem:

cd subdir && $(MAKE)

其等價於:

subsystem:

$(MAKE) -C subdir

定義$(MAKE)宏變量的意思是,也許我們的make需要一些參數,所以定義成一個變量比較利於維護。這兩個例子的意思都是先進入「subdir」目錄,然後執行make命令。

我們把這個Makefile叫做「總控Makefile」,總控Makefile的變量可以傳遞到下級的Makefile中(如果你顯示的宣告),但是不會覆蓋下層的Makefile中所定義的變量,除非指定了「-e」參數。

如果你要傳遞變量到下級Makefile中,那麼你可以使用這樣的宣告:

export <variable ...>

如果你不想讓某些變量傳遞到下級Makefile中,那麼你可以這樣宣告:

unexport <variable ...>

如:

範例一:

export variable = value

其等價於:

variable = value

export variable

其等價於:

export variable := value

其等價於:

variable := value

export variable

範例二:

export variable += value

其等價於:

variable += value

export variable

如果你要傳遞所有的變量,那麼,只要一個export就行了。後面什麼也不用跟,表示傳遞所有的變量。

需要注意的是,有兩個變量,一個是SHELL,一個是MAKEFLAGS,這兩個變量不管你是否export,其總是要傳遞到下層Makefile中,特別是MAKEFILES變量,其中包含了make的參數訊息,如果我們執行「總控 Makefile」時有make參數或是在上層Makefile中定義了這個變量,那麼MAKEFILES變量將會是這些參數,並會傳遞到下層 Makefile中,這是一個系統級的環境變量。

但是make命令中的有幾個參數並不往下傳遞,它們是「-C」,「-f」,「-h」「-o」和「-W」(有關Makefile參數的細節將在後面說明),如果你不想往下層傳遞參數,那麼,你可以這樣來:

subsystem:

cd subdir && $(MAKE) MAKEFLAGS=

如果你定義了環境變量MAKEFLAGS,那麼你得確信其中的選項是大家都會用到的,如果其中有「-t」,「-n」,和「-q」參數,那麼將會有讓你意想不到的結果,或許會讓你異常地恐慌。

還有一個在「巢狀執行」中比較有用的參數,「-w」或是「--print- directory」會在make的過程中輸出一些訊息,讓你看到目前的工作目錄。比如,如果我們的下級make目錄是「/home/hchen/gnu/make」,如果我們使用「make -w」來執行,那麼當進入該目錄時,我們會看到:

make: Entering directory `/home/hchen/gnu/make'.

而在完成下層make後離開目錄時,我們會看到:

make: Leaving directory `/home/hchen/gnu/make'

當你使用「-C」參數來指定make下層Makefile時,「-w」會被自動打開的。如果參數中有「-s」(「--slient」)或是「--no-print-directory」,那麼,「-w」總是失效的。

五、定義命令包

如果Makefile中出現一些相同命令序列,那麼我們可以為這些相同的命令序列定義一個變量。定義這種命令序列的語法以「define」開始,以「endef」結束,如:

define run-yacc

yacc $(firstword $^)

mv y.tab.c $@

endef

這裡,「run-yacc」是這個命令包的名字,其不要和Makefile中的變量重名。在「define」和「endef」中的兩行就是命令序列。這個命令包中的第一個命令是運行Yacc程序,因為Yacc程序總是生成「y.tab.c」的檔案,所以第二行的命令就是把這個檔案改改名字。還是把這個命令包放到一個範例中來看看吧。

foo.c : foo.y

$(run-yacc)

我們可以看見,要使用這個命令包,我們就好像使用變量一樣。在這個命令包的使用中,命令包「run-yacc」中的「$^」就是「foo.y」,「$@」就是「foo.c」(有關這種以「$」開頭的特殊變量,我們會在後面介紹),make在執行命令包時,命令包中的每個命令會被依次獨立執行。

使用變量

————

在Makefile中的定義的變量,就像是C/C++語言中的宏一樣,他代表了一個文本字串,在Makefile中執行的時候其會自動原模原樣地展開在所使用的地方。其與C/C++所不同的是,你可以在Makefile中改變其值。在 Makefile中,變量可以使用在「目標」,「依賴目標」,「命令」或是Makefile的其它部分中。

變量的命名字可以包含字符、數字,下劃線(可以是數字開頭),但不應該含有「:」、「#」、「=」或是空字符(空格、Return等)。變量是大小寫敏感的,「foo」、「Foo」和「FOO」是三個不同的變量名。傳統的Makefile的變量名是全大寫的命名方式,但我推薦使用大小寫搭配的變量名,如:MakeFlags。這樣可以避免和系統的變量衝突,而發生意外的事情。

有一些變量是很奇怪字串,如「$<」、「$@」等,這些是自動化變量,我會在後面介紹。

一、變量的基礎

變量在宣告時需要給予初值,而在使用時,需要給在變量名前加上「$」符號,但最好用小括號「()」或是大括號「{}」把變量給包括起來。如果你要使用真實的「$」字符,那麼你需要用「$$」來表示。

變量可以使用在許多地方,如規則中的「目標」、「依賴」、「命令」以及新的變量中。先看一個例子:

objects = program.o foo.o utils.o

program : $(objects)

cc -o program $(objects)

$(objects) : defs.h

變量會在使用它的地方精確地展開,就像C/C++中的宏一樣,例如:

foo = c

prog.o : prog.$(foo)

$(foo)$(foo) -$(foo) prog.$(foo)

展開後得到:

prog.o : prog.c

cc -c prog.c

當然,千萬不要在你的Makefile中這樣干,這裡只是舉個例子來表明Makefile中的變量在使用處展開的真實樣子。可見其就是一個「替代」的原理。

另外,給變量加上括號完全是為了更加安全地使用這個變量,在上面的例子中,如果你不想給變量加上括號,那也可以,但我還是強烈建議你給變量加上括號。

二、變量中的變量

在定義變量的值時,我們可以使用其它變量來構造變量的值,在Makefile中有兩種方式來在用變量定義變量的值。

先看第一種方式,也就是簡單的使用「=」號,在「=」左側是變量,右側是變量的值,右側變量的值可以定義在檔案的任何一處,也就是說,右側中的變量不一定非要是已定義好的值,其也可以使用後面定義的值。如:

foo = $(bar)

bar = $(ugh)

ugh = Huh?

all:

echo $(foo)

我們執行「make all」將會打出變量$(foo)的值是「Huh?」( $(foo)的值是$(bar),$(bar)的值是$(ugh),$(ugh)的值是「Huh?」)可見,變量是可以使用後面的變量來定義的。

這個功能有好的地方,也有不好的地方,好的地方是,我們可以把變量的真實值推到後面來定義,如:

CFLAGS = $(include_dirs) -O

include_dirs = -Ifoo -Ibar

當「CFLAGS」在命令中被展開時,會是「-Ifoo -Ibar -O」。但這種形式也有不好的地方,那就是遞歸定義,如:

CFLAGS = $(CFLAGS) -O

或:

A = $(B)

B = $(A)

這會讓make陷入無限的變量展開過程中去,當然,我們的make是有能力檢測這樣的定義,並會報錯。還有就是如果在變量中使用函數,那麼,這種方式會讓我們的make運行時非常慢,更糟糕的是,他會使用得兩個make的函數「wildcard」和「shell」發生不可預知的錯誤。因為你不會知道這兩個函數會被呼叫多少次。

為了避免上面的這種方法,我們可以使用make中的另一種用變量來定義變量的方法。這種方法使用的是「:=」操作符,如:

x := foo

y := $(x) bar

x := later

其等價於:

y := foo bar

x := later

值得一提的是,這種方法,前面的變量不能使用後面的變量,只能使用前面已定義好了的變量。如果是這樣:

y := $(x) bar

x := foo

那麼,y的值是「bar」,而不是「foo bar」。

上面都是一些比較簡單的變量使用了,讓我們來看一個複雜的例子,其中包括了make的函數、條件表達式和一個系統變量「MAKELEVEL」的使用:

ifeq (0,${MAKELEVEL})

cur-dir := $(shell pwd)

whoami := $(shell whoami)

host-type := $(shell arch)

MAKE := ${MAKE} host-type=${host-type} whoami=${whoami}

endif

關於條件表達式和函數,我們在後面再說,對於系統變量「MAKELEVEL」,其意思是,如果我們的make有一個巢狀執行的動作(參見前面的「巢狀使用make」),那麼,這個變量會記錄了我們的當前Makefile的呼叫層數。

下面再介紹兩個定義變量時我們需要知道的,請先看一個例子,如果我們要定義一個變量,其值是一個空格,那麼我們可以這樣來:

nullstring :=

space := $(nullstring) # end of the line

nullstring是一個Empty變量,其中什麼也沒有,而我們的space的值是一個空格。因為在操作符的右邊是很難描述一個空格的,這裡採用的技術很管用,先用一個Empty變量來標明變量的值開始了,而後面採用「#」註釋符來表示變量定義的終止,這樣,我們可以定義出其值是一個空格的變量。請注意這裡關於「#」的使用,註釋符「#」的這種特性值得我們注意,如果我們這樣定義一個變量:

dir := /foo/bar # directory to put the frobs in

dir這個變量的值是「/foo/bar」,後面還跟了4個空格,如果我們這樣使用這樣變量來指定別的目錄——「$(dir)/file」那麼就完蛋了。

還有一個比較有用的操作符是「?=」,先看範例:

FOO ?= bar

其含義是,如果FOO沒有被定義過,那麼變量FOO的值就是「bar」,如果FOO先前被定義過,那麼這條語將什麼也不做,其等價於:

ifeq ($(origin FOO), undefined)

FOO = bar

endif

三、變量高級用法

這裡介紹兩種變量的高級使用方法,第一種是變量值的替換。

我們可以替換變量中的共有的部分,其格式是「$(var:a=b)」或是「${var:a=b}」,其意思是,把變量「var」中所有以「a」字串「結尾」的「a」替換成「b」字串。這裡的「結尾」意思是「空格」或是「結束符」。

還是看一個範例吧:

foo := a.o b.o c.o

bar := $(foo:.o=.c)

這個範例中,我們先定義了一個「$(foo)」變量,而第二行的意思是把「$(foo)」中所有以「.o」字串「結尾」全部替換成「.c」,所以我們的「$(bar)」的值就是「a.c b.c c.c」。

另外一種變量替換的技術是以「靜態模式」(參見前面章節)定義的,如:

foo := a.o b.o c.o

bar := $(foo:%.o=%.c)

這依賴於被替換字串中的有相同的模式,模式中必須包含一個「%」字符,這個例子同樣讓$(bar)變量的值為「a.c b.c c.c」。

第二種高級用法是——「把變量的值再當成變量」。先看一個例子:

x = y

y = z

a := $($(x))

在這個例子中,$(x)的值是「y」,所以$($(x))就是$(y),於是$(a)的值就是「z」。(注意,是「x=y」,而不是「x=$(y)」)

我們還可以使用更多的層次:

x = y

y = z

z = u

a := $($($(x)))

這裡的$(a)的值是「u」,相關的推導留給讀者自己去做吧。

讓我們再複雜一點,使用上「在變量定義中使用變量」的第一個方式,來看一個例子:

x = $(y)

y = z

z = Hello

a := $($(x))

這裡的$($(x))被替換成了$($(y)),因為$(y)值是「z」,所以,最終結果是:a:=$(z),也就是「Hello」。

再複雜一點,我們再加上函數:

x = variable1

variable2 := Hello

y = $(subst 1,2,$(x))

z = y

a := $($($(z)))

這個例子中,「$($($(z)))」擴展為「$($(y))」,而其再次被擴展為「$($ (subst 1,2,$(x)))」。$(x)的值是「variable1」,subst函數把「variable1」中的所有「1」字串替換成「2」字串,於是,「variable1」變成「variable2」,再取其值,所以,最終,$(a)的值就是$(variable2)的值——「Hello」。(喔,好不容易)

在這種方式中,或要可以使用多個變量來組成一個變量的名字,然後再取其值:

first_second = Hello

a = first

b = second

all = $($a_$b)

這裡的「$a_$b」組成了「first_second」,於是,$(all)的值就是「Hello」。

再來看看結闔第一種技術的例子:

a_objects := a.o b.o c.o

1_objects := 1.o 2.o 3.o

sources := $($(a1)_objects:.o=.c)

這個例子中,如果$(a1)的值是「a」的話,那麼,$(sources)的值就是「a.c b.c c.c」;如果$(a1)的值是「1」,那麼$(sources)的值是「1.c 2.c 3.c」。

再來看一個這種技術和「函數」與「條件語句」一同使用的例子:

ifdef do_sort

func := sort

else

func := strip

endif

bar := a d b g q c

foo := $($(func) $(bar))

這個範例中,如果定義了「do_sort」,那麼:foo := $(sort a d b g q c),於是$(foo)的值就是「a b c d g q」,而如果沒有定義「do_sort」,那麼:foo := $(sort a d b g q c),呼叫的就是strip函數。

當然,「把變量的值再當成變量」這種技術,同樣可以用在操作符的左邊:

dir = foo

$(dir)_sources := $(wildcard $(dir)/*.c)

define $(dir)_print

lpr $($(dir)_sources)

endef

這個例子中定義了三個變量:「dir」,「foo_sources」和「foo_print」。

四、追加變量值

我們可以使用「+=」操作符給變量追加值,如:

objects = main.o foo.o bar.o utils.o

objects += another.o

於是,我們的$(objects)值變成:「main.o foo.o bar.o utils.o another.o」(another.o被追加進去了)

使用「+=」操作符,可以模擬為下面的這種例子:

objects = main.o foo.o bar.o utils.o

objects := $(objects) another.o

所不同的是,用「+=」更為簡潔。

如果變量之前沒有定義過,那麼,「+=」會自動變成「=」,如果前面有變量定義,那麼「+=」會繼承於前次操作的賦值符。如果前一次的是「:=」,那麼「+=」會以「:=」作為其賦值符,如:

variable := value

variable += more

等價於:

variable := value

variable := $(variable) more

但如果是這種情況:

variable = value

variable += more

由於前次的賦值符是「=」,所以「+=」也會以「=」來做為賦值,那麼豈不會發生變量的遞補歸定義,這是很不好的,所以make會自動為我們解決這個問題,我們不必擔心這個問題。

五、override 指示符

如果有變量是通常make的命令行參數設置的,那麼Makefile中對這個變量的賦值會被忽略。如果你想在Makefile中設置這類參數的值,那麼,你可以使用「override」指示符。其語法是:

override <variable> = <value>

override <variable> := <value>

當然,你還可以追加:

override <variable> += <more text>

對於多行的變量定義,我們用define指示符,在define指示符前,也同樣可以使用ovveride指示符,如:

override define foo

bar

endef

六、多行變量

還有一種設置變量值的方法是使用define關鍵字。使用define關鍵字設置變量的值可以有換行,這有利於定義一系列的命令(前面我們講過「命令包」的技術就是利用這個關鍵字)。

define指示符後面跟的是變量的名字,而重起一行定義變量的值,定義是以endef關鍵字結束。其工作方式和「=」操作符一樣。變量的值可以包含函數、命令、文字,或是其它變量。因為命令需要以[Tab]鍵開頭,所以如果你用define定義的命令變量中沒有以[Tab]鍵開頭,那麼make就不會把其認為是命令。

下面的這個範例展示了define的用法:

define two-lines

echo foo

echo $(bar)

endef

七、環境變量

make運行時的系統環境變量可以在make開始運行時被載入到Makefile檔案中,但是如果Makefile中已定義了這個變量,或是這個變量由make命令行帶入,那麼系統的環境變量的值將被覆蓋。(如果make指定了「-e」參數,那麼,系統環境變量將覆蓋Makefile中定義的變量)

因此,如果我們在環境變量中設置了「CFLAGS」環境變量,那麼我們就可以在所有的 Makefile中使用這個變量了。這對於我們使用統一的編譯參數有比較大的好處。如果Makefile中定義了CFLAGS,那麼則會使用 Makefile中的這個變量,如果沒有定義則使用系統環境變量的值,一個共性和個性的統一,很像「全域變量」和「局部變量」的特性。

當make巢狀呼叫時(參見前面的「巢狀呼叫」章節),上層Makefile中定義的變量會以系統環境變量的方式傳遞到下層的Makefile中。當然,預設情況下,只有通過命令行設置的變量會被傳遞。而定義在檔案中的變量,如果要向下層 Makefile傳遞,則需要使用exprot關鍵字來宣告。(參見前面章節)

當然,我並不推薦把許多的變量都定義在系統環境中,這樣,在我們執行不用的Makefile時,擁有的是同一套系統變量,這可能會帶來更多的麻煩。

八、目標變量

前面我們所講的在Makefile中定義的變量都是「全域變量」,在整個檔案,我們都可以訪問這些變量。當然,「自動化變量」除外,如「$<」等這種類量的自動化變量就屬於「規則型變量」,這種變量的值依賴於規則的目標和依賴目標的定義。

當然,我樣同樣可以為某個目標設置局部變量,這種變量被稱為「Target-specific Variable」,它可以和「全域變量」同名,因為它的作用範圍只在這條規則以及連帶規則中,所以其值也只在作用範圍內有效。而不會影響規則鏈以外的全域變量的值。

其語法是:

<target ...> : <variable-assignment>

<target ...> : overide <variable-assignment>

<variable-assignment>可以是前面講過的各種賦值表達式,如「=」、「:=」、「+=」或是「?=」。第二個語法是針對於make命令行帶入的變量,或是系統環境變量。

這個特性非常的有用,當我們設置了這樣一個變量,這個變量會作用到由這個目標所引發的所有的規則中去。如:

prog : CFLAGS = -g

prog : prog.o foo.o bar.o

$(CC) $(CFLAGS) prog.o foo.o bar.o

prog.o : prog.c

$(CC) $(CFLAGS) prog.c

foo.o : foo.c

$(CC) $(CFLAGS) foo.c

bar.o : bar.c

$(CC) $(CFLAGS) bar.c

在這個範例中,不管全域的$(CFLAGS)的值是什麼,在prog目標,以及其所引發的所有規則中(prog.o foo.o bar.o的規則),$(CFLAGS)的值都是「-g」

九、模式變量

在GNU的make中,還支持模式變量(Pattern-specific Variable),通過上面的目標變量中,我們知道,變量可以定義在某個目標上。模式變量的好處就是,我們可以給定一種「模式」,可以把變量定義在符合這種模式的所有目標上。

我們知道,make的「模式」一般是至少含有一個「%」的,所以,我們可以以如下方式給所有以[.o]結尾的目標定義目標變量:

%.o : CFLAGS = -O

同樣,模式變量的語法和「目標變量」一樣:

<pattern ...> : <variable-assignment>

<pattern ...> : override <variable-assignment>

override同樣是針對於系統環境傳入的變量,或是make命令行指定的變量。

使用條件判斷

——————

使用條件判斷,可以讓make根據運行時的不同情況選擇不同的執行分支。條件表達式可以是比較變量的值,或是比較變量和常量的值。

一、範例

下面的例子,判斷$(CC)變量是否「gcc」,如果是的話,則使用GNU函數編譯目標。

libs_for_gcc = -lgnu

normal_libs =

foo: $(objects)

ifeq ($(CC),gcc)

$(CC) -o foo $(objects) $(libs_for_gcc)

else

$(CC) -o foo $(objects) $(normal_libs)

endif

可見,在上面範例的這個規則中,目標「foo」可以根據變量「$(CC)」值來選取不同的函數庫來編譯程序。

我們可以從上面的範例中看到三個關鍵字:ifeq、else和endif。ifeq的意思表示條件語句的開始,並指定一個條件表達式,表達式包含兩個參數,以逗號分隔,表達式以圓括號括起。else表示條件表達式為假的情況。endif表示一個條件語句的結束,任何一個條件表達式都應該以endif結束。

當我們的變量$(CC)值是「gcc」時,目標foo的規則是:

foo: $(objects)

$(CC) -o foo $(objects) $(libs_for_gcc)

而當我們的變量$(CC)值不是「gcc」時(比如「cc」),目標foo的規則是:

foo: $(objects)

$(CC) -o foo $(objects) $(normal_libs)

當然,我們還可以把上面的那個例子寫得更簡潔一些:

libs_for_gcc = -lgnu

normal_libs =

ifeq ($(CC),gcc)

libs=$(libs_for_gcc)

else

libs=$(normal_libs)

endif

foo: $(objects)

$(CC) -o foo $(objects) $(libs)

二、語法

條件表達式的語法為:

<conditional-directive>

<text-if-true>

endif

以及:

<conditional-directive>

<text-if-true>

else

<text-if-false>

endif

其中<conditional-directive>表示條件關鍵字,如「ifeq」。這個關鍵字有四個。

第一個是我們前面所見過的「ifeq」

ifeq (<arg1>, <arg2>)

ifeq '<arg1>' '<arg2>'

ifeq "<arg1>" "<arg2>"

ifeq "<arg1>" '<arg2>'

ifeq '<arg1>' "<arg2>"

比較參數「arg1」和「arg2」的值是否相同。當然,參數中我們還可以使用make的函數。如:

ifeq ($(strip $(foo)),)

<text-if-empty>

endif

這個範例中使用了「strip」函數,如果這個函數的返回值是空(Empty),那麼<text-if-empty>就生效。

第二個條件關鍵字是「ifneq」。語法是:

ifneq (<arg1>, <arg2>)

ifneq '<arg1>' '<arg2>'

ifneq "<arg1>" "<arg2>"

ifneq "<arg1>" '<arg2>'

ifneq '<arg1>' "<arg2>"

其比較參數「arg1」和「arg2」的值是否相同,如果不同,則為真。和「ifeq」類似。

第三個條件關鍵字是「ifdef」。語法是:

ifdef <variable-name>

如果變量<variable-name>的值非空,那到表達式為真。否則,表達式為假。當然,<variable-name>同樣可以是一個函數的返回值。注意,ifdef只是測試一個變量是否有值,其並不會把變量擴展到當前位置。還是來看兩個例子:

範例一:

bar =

foo = $(bar)

ifdef foo

frobozz = yes

else

frobozz = no

endif

範例二:

foo =

ifdef foo

frobozz = yes

else

frobozz = no

endif

第一個例子中,「$(frobozz)」值是「yes」,第二個則是「no」。

第四個條件關鍵字是「ifndef」。其語法是:

ifndef <variable-name>

這個我就不多說了,和「ifdef」是相反的意思。

在<conditional-directive>這一行上,多餘的空格是被允許的,但是不能以[Tab]鍵做為開始(不然就被認為是命令)。而註釋符「#」同樣也是安全的。「else」和「endif」也一樣,只要不是以[Tab]鍵開始就行了。

特別注意的是,make是在讀取Makefile時就計算條件表達式的值,並根據條件表達式的值來選擇語句,所以,你最好不要把自動化變量(如「$@」等)放入條件表達式中,因為自動化變量是在運行時才有的。

而且,為了避免混亂,make不允許把整個條件語句分成兩部分放在不同的檔案中。

使用函數

————

在Makefile中可以使用函數來處理變量,從而讓我們的命令或是規則更為的靈活和具有智能。make所支持的函數也不算很多,不過已經足夠我們的操作了。函數呼叫後,函數的返回值可以當做變量來使用。

一、函數的呼叫語法

函數呼叫,很像變量的使用,也是以「$」來標識的,其語法如下:

$(<function> <arguments>)

或是

${<function> <arguments>}

這裡,<function>就是函數名,make支持的函數不多。< arguments>是函數的參數,參數間以逗號「,」分隔,而函數名和參數之間以「空格」分隔。函數呼叫以「$」開頭,以圓括號或花括號把函數名和參數括起。感覺很像一個變量,是不是?函數中的參數可以使用變量,為了風格的統一,函數和變量的括號最好一樣,如使用「$(subst a,b,$(x))」這樣的形式,而不是「$(subst a,b,${x})」的形式。因為統一會更清楚,也會減少一些不必要的麻煩。

還是來看一個範例:

comma:= ,

empty:=

space:= $(empty) $(empty)

foo:= a b c

bar:= $(subst $(space),$(comma),$(foo))

在這個範例中,$(comma)的值是一個逗號。$(space)使用了$(empty)定義了一個空格,$(foo)的值是「a b c」,$(bar)的定義用,呼叫了函數「subst」,這是一個替換函數,這個函數有三個參數,第一個參數是被替換字串,第二個參數是替換字串,第三個參數是替換操作作用的字串。這個函數也就是把$(foo)中的空格替換成逗號,所以$(bar)的值是「a,b,c」。

二、字串處理函數

$(subst <from>,<to>,<text>)

名稱:字串替換函數——subst。

功能:把字串<text>中的<from>字串替換成<to>。

返回:函數返回被替換過後的字串。

範例:

$(subst ee,EE,feet on the street),

把「feet on the street」中的「ee」替換成「EE」,返回結果是「fEEt on the strEEt」。

$(patsubst <pattern>,<replacement>,<text>)

名稱:模式字串替換函數——patsubst。

功能:查找<text>中的單詞(單詞以「空格」、「Tab」或「Return」「換行」分隔)是否符合模式<pattern>,如果匹配的話,則以<replacement>替換。這裡,<pattern>可以包括通配符「%」,表示任意長度的字串。如果 <replacement>中也包含「%」,那麼,<replacement>中的這個「%」將是< pattern>中的那個「%」所代表的字串。(可以用「\」來轉義,以「\%」來表示真實含義的「%」字符)

返回:函數返回被替換過後的字串。

範例:

$(patsubst %.c,%.o,x.c.c bar.c)

把字串「x.c.c bar.c」符合模式[%.c]的單詞替換成[%.o],返回結果是「x.c.o bar.o」

備註:

這和我們前面「變量章節」說過的相關知識有點相似。如:

「$(var:<pattern>=<replacement>)」

相當於

「$(patsubst <pattern>,<replacement>,$(var))」,

而「$(var: <suffix>=<replacement>)」

則相當於

「$(patsubst %<suffix>,%<replacement>,$(var))」。

例如有:objects = foo.o bar.o baz.o,

那麼,「$(objects:.o=.c)」和「$(patsubst %.o,%.c,$(objects))」是一樣的。

$(strip <string>)

名稱:去空格函數——strip。

功能:去掉<string>字串中開頭和結尾的空字符。

返回:返回被去掉空格的字串值。

範例:

$(strip a b c )

把字串「a b c 」去到開頭和結尾的空格,結果是「a b c」。

$(findstring <find>,<in>)

名稱:查找字串函數——findstring。

功能:在字串<in>中查找<find>字串。

返回:如果找到,那麼返回<find>,否則返回空字串。

範例:

$(findstring a,a b c)

$(findstring a,b c)

第一個函數返回「a」字串,第二個返回「」字串(空字串)

$(filter <pattern...>,<text>)

名稱:過濾函數——filter。

功能:以<pattern>模式過濾<text>字串中的單詞,保留符合模式<pattern>的單詞。可以有多個模式。

返回:返回符合模式<pattern>的字串。

範例:

sources := foo.c bar.c baz.s ugh.h

foo: $(sources)

cc $(filter %.c %.s,$(sources)) -o foo

$(filter %.c %.s,$(sources))返回的值是「foo.c bar.c baz.s」。

$(filter-out <pattern...>,<text>)

名稱:反過濾函數——filter-out。

功能:以<pattern>模式過濾<text>字串中的單詞,去除符合模式<pattern>的單詞。可以有多個模式。

返回:返回不符合模式<pattern>的字串。

範例:

objects=main1.o foo.o main2.o bar.o

mains=main1.o main2.o

$(filter-out $(mains),$(objects)) 返回值是「foo.o bar.o」。

$(sort <list>)

名稱:排序函數——sort。

功能:給字串<list>中的單詞排序(升序)。

返回:返回排序後的字串。

範例:$(sort foo bar lose)返回「bar foo lose」 。

備註:sort函數會去掉<list>中相同的單詞。

$(word <n>,<text>)

名稱:取單詞函數——word。

功能:取字串<text>中第<n>個單詞。(從一開始)

返回:返回字串<text>中第<n>個單詞。如果<n>比<text>中的單詞數要大,那麼返回空字串。

範例:$(word 2, foo bar baz)返回值是「bar」。

$(wordlist <s>,<e>,<text>)

名稱:取單詞串函數——wordlist。

功能:從字串<text>中取從<s>開始到<e>的單詞串。<s>和<e>是一個數字。

返回:返回字串<text>中從<s>到<e>的單詞字串。如果<s>比<text>中的單詞數要大,那麼返回空字串。如果<e>大於<text>的單詞數,那麼返回從<s>開始,到< text>結束的單詞串。

範例: $(wordlist 2, 3, foo bar baz)返回值是「bar baz」。

$(words <text>)

名稱:單詞個數統計函數——words。

功能:統計<text>中字串中的單詞個數。

返回:返回<text>中的單詞數。

範例:$(words, foo bar baz)返回值是「3」。

備註:如果我們要取<text>中最後的一個單詞,我們可以這樣:$(word $(words <text>),<text>)。

$(firstword <text>)

名稱:首單詞函數——firstword。

功能:取字串<text>中的第一個單詞。

返回:返回字串<text>的第一個單詞。

範例:$(firstword foo bar)返回值是「foo」。

備註:這個函數可以用word函數來實現:$(word 1,<text>)。

以上,是所有的字串操作函數,如果搭配混合使用,可以完成比較複雜的功能。這裡,舉一個現實中應用的例子。我們知道,make使用「VPATH」變量來指定「相依性檔案」的搜索路徑。於是,我們可以利用這個搜索路徑來指定編譯器對頭檔案的搜索路徑參數CFLAGS,如:

override CFLAGS += $(patsubst %,-I%,$(subst :, ,$(VPATH)))

如果我們的「$(VPATH)」值是「src:../headers」,那麼「$(patsubst %,-I%,$(subst :, ,$(VPATH)))」將返回「-Isrc -I../headers」,這正是cc或gcc搜索頭檔案路徑的參數。

三、檔案名操作函數

下面我們要介紹的函數主要是處理檔案名的。每個函數的參數字串都會被當做一個或是一系列的檔案名來對待。

$(dir <names...>)

名稱:取目錄函數——dir。

功能:從檔案名序列<names>中取出目錄部分。目錄部分是指最後一個反斜線(「/」)之前的部分。如果沒有反斜線,那麼返回「./」。

返回:返回檔案名序列<names>的目錄部分。

範例: $(dir src/foo.c hacks)返回值是「src/ ./」。

$(notdir <names...>)

名稱:取檔案函數——notdir。

功能:從檔案名序列<names>中取出非目錄部分。非目錄部分是指最後一個反斜線(「/」)之後的部分。

返回:返回檔案名序列<names>的非目錄部分。

範例: $(notdir src/foo.c hacks)返回值是「foo.c hacks」。

$(suffix <names...>)

名稱:取後綴函數——suffix。

功能:從檔案名序列<names>中取出各個檔案名的後綴。

返回:返回檔案名序列<names>的後綴序列,如果檔案沒有後綴,則返回空字串。

範例:$(suffix src/foo.c src-1.0/bar.c hacks)返回值是「.c .c」。

$(basename <names...>)

名稱:取前綴函數——basename。

功能:從檔案名序列<names>中取出各個檔案名的前綴部分。

返回:返回檔案名序列<names>的前綴序列,如果檔案沒有前綴,則返回空字串。

範例:$(basename src/foo.c src-1.0/bar.c hacks)返回值是「src/foo src-1.0 /bar hacks」。

$(addsuffix <suffix>,<names...>)

名稱:加後綴函數——addsuffix。

功能:把後綴<suffix>加到<names>中的每個單詞後面。

返回:返回加過後綴的檔案名序列。

範例:$(addsuffix .c,foo bar)返回值是「foo.c bar.c」。

$(addprefix <prefix>,<names...>)

名稱:加前綴函數——addprefix。

功能:把前綴<prefix>加到<names>中的每個單詞後面。

返回:返回加過前綴的檔案名序列。

範例:$(addprefix src/,foo bar)返回值是「src/foo src/bar」。

$(join <list1>,<list2>)

名稱:連接函數——join。

功能:把<list2>中的單詞對應地加到<list1>的單詞後面。如果<list1>的單詞個數要比< list2>的多,那麼,<list1>中的多出來的單詞將保持原樣。如果<list2>的單詞個數要比< list1>多,那麼,<list2>多出來的單詞將被覆制到<list2>中。

返回:返回連接過後的字串。

範例:$(join aaa bbb , 111 222 333)返回值是「aaa111 bbb222 333」。

四、foreach 函數

foreach函數和別的函數非常的不一樣。因為這個函數是用來做循環用的, Makefile中的 foreach函數幾乎是仿照於Unix標準 Shell(/bin/sh )中的for語句,或是 C-Shell(/bin/csh)中的 foreach語句而構建的。它的語法是:

$(foreach <var>,<list>,<text>)

這個函數的意思是,把參數<list> 中的單詞逐一取出放到參數<var>所指定的變量中,然後再執行 <text>所包含的表達式。每一次<text> 會返回一個字串,循環過程中,<text>的所返回的每個字串會以空格分隔,最後當整個循環結束時, <text>所返回的每個字串所組成的整個字串(以空格分隔)將會是foreach 函數的返回值。

所以,<var> 最好是一個變量名,<list>可以是一個表達式,而 <text>中一般會使用<var>這個參數來依次枚舉 <list>中的單詞。舉個例子:

names := a b c d

files := $(foreach n,$(names),$(n).o)

上面的例子中,$(name) 中的單詞會被挨個取出,並存到變量「n」中,「 $(n).o」每次根據「$(n)」計算出一個值,這些值以空格分隔,最後作為 foreach函數的返回,所以, $(files)的值是「a.o b.o c.o d.o」。

注意,foreach 中的<var>參數是一個臨時的局部變量, foreach函數執行完後,參數<var>的變量將不在作用,其作用域只在 foreach函數當中。

五、if 函數

if函數很像 GNU的make所支持的條件語句—— ifeq(參見前面所述的章節), if函數的語法是:

$(if <condition>,<then-part>)

或是

$(if <condition>,<then-part>,<else-part>)

可見,if 函數可以包含「else」部分,或是不含。即 if函數的參數可以是兩個,也可以是三個。<condition> 參數是if的表達式,如果其返回的為非空字串,那麼這個表達式就相當於返回真,於是, <then-part>會被計算,否則<else-part> 會被計算。

而if 函數的返回值是,如果<condition>為真(非空字串),那個 <then-part>會是整個函數的返回值,如果<condition> 為假(空字串),那麼<else-part>會是整個函數的返回值,此時如果 <else-part>沒有被定義,那麼,整個函數返回空字串。

所以,<then-part> 和<else-part>只會有一個被計算。

六、call函數

call函數是唯一一個可以用來建立新的參數化的函數。你可以寫一個非常複雜的表達式,這個表達式中,你可以定義許多參數,然後你可以用 call函數來向這個表達式傳遞參數。其語法是:

$(call <expression>,<parm1>,<parm2>,<parm3>...)

當make 執行這個函數時,<expression>參數中的變量,如 $(1),$(2), $(3)等,會被參數<parm1>, <parm2>, <parm3>依次取代。而<expression> 的返回值就是call函數的返回值。例如:

reverse = $(1) $(2)

foo = $(call reverse,a,b)

那麼,foo 的值就是「a b」。當然,參數的次序是可以自定義的,不一定是順序的,如:

reverse = $(2) $(1)

foo = $(call reverse,a,b)

此時的foo 的值就是「b a」。

七、origin函數

origin函數不像其它的函數,他並不操作變量的值,他只是告訴你你的這個變量是哪裡來的?其語法是:

$(origin <variable>)

注意,<variable> 是變量的名字,不應該是引用。所以你最好不要在<variable>中使用「 $」字符。Origin函數會以其返回值來告訴你這個變量的「出生情況」,下面,是 origin函數的返回值 :

「undefined 」

如果 <variable>從來沒有定義過, origin函數返回這個值「undefined」。

「default 」

如果 <variable>是一個預設的定義,比如「 CC」這個變量,這種變量我們將在後面講述。

「environment 」

如果 <variable>是一個環境變量,並且當 Makefile被執行時,「-e」參數沒有被打開。

「file 」

如果 <variable>這個變量被定義在 Makefile中。

「command line 」

如果 <variable>這個變量是被命令行定義的。

「override 」

如果 <variable>是被 override指示符重新定義的。

「automatic 」

如果 <variable>是一個命令運行中的自動化變量。關於自動化變量將在後面講述。

這些訊息對於我們編寫Makefile 是非常有用的,例如,假設我們有一個Makefile其包含了一個定義檔案 Make.def,在Make.def中定義了一個變量「 bletch」,而我們的環境中也有一個環境變量「 bletch」,此時,我們想判斷一下,如果變量來源於環境,那麼我們就把之重定義了,如果來源於Make.def 或是命令行等非環境的,那麼我們就不重新定義它。於是,在我們的Makefile中,我們可以這樣寫:

ifdef bletch

ifeq "$(origin bletch)" "environment"

bletch = barf, gag, etc.

endif

endif

當然,你也許會說,使用override 關鍵字不就可以重新定義環境中的變量了嗎?為什麼需要使用這樣的步驟?是的,我們用override是可以達到這樣的效果,可是 override過於粗暴,它同時會把從命令行定義的變量也覆蓋了,而我們只想重新定義環境傳來的,而不想重新定義命令行傳來的。

八、shell函數

shell函數也不像其它的函數。顧名思義,它的參數應該就是作業系統 Shell的命令。它和反引號「 `」是相同的功能。這就是說,shell函數把執行作業系統命令後的輸出作為函數返回。於是,我們可以用作業系統命令以及字串處理命令 awk, sed等等命令來生成一個變量,如:

contents := $(shell cat foo)

files := $(shell echo *.c)

注意,這個函數會新生成一個Shell 程序來執行命令,所以你要注意其運行性能,如果你的Makefile中有一些比較複雜的規則,並大量使用了這個函數,那麼對於你的系統性能是有害的。特別是 Makefile的隱晦的規則可能會讓你的 shell函數執行的次數比你想像的多得多。

九、控制make的函數

make提供了一些函數來控制 make的運行。通常,你需要檢測一些運行Makefile時的運行時訊息,並且根據這些訊息來決定,你是讓 make繼續執行,還是停止。

$(error <text ...>)

產生一個致命的錯誤, <text ...>是錯誤訊息。注意, error函數不會在一被使用就會產生錯誤訊息,所以如果你把其定義在某個變量中,並在後續的腳本中使用這個變量,那麼也是可以的。例如:

範例一:

ifdef ERROR_001

$(error error is $(ERROR_001))

endif

範例二:

ERR = $(error found an error!)

.PHONY: err

err: ; $(ERR)

範例一會在變量 ERROR_001定義了後執行時產生 error呼叫,而範例二則在目錄err被執行時才發生 error呼叫。

$(warning <text ...>)

這個函數很像 error函數,只是它並不會讓 make退出,只是輸出一段警告訊息,而make繼續執行。

make 的運行

——————

一般來說,最簡單的就是直接在命令行下輸入make命令,make命令會找當前目錄的 makefile來執行,一切都是自動的。但也有時你也許只想讓make重編譯某些檔案,而不是整個專案,而又有的時候你有幾套編譯規則,你想在不同的時候使用不同的編譯規則,等等。本章節就是講述如何使用make命令的。

一、make的退出碼

make命令執行後有三個退出碼:

0 —— 表示成功執行。

1 —— 如果make運行時出現任何錯誤,其返回1。

2 —— 如果你使用了make的「-q」選項,並且make使得一些目標不需要更新,那麼返回2。

Make的相關參數我們會在後續章節中講述。

二、指定Makefile

前面我們說過,GNU make找尋預設的Makefile的規則是在當前目錄下依次找三個檔案——「GNUmakefile」、「makefile」和「Makefile」。其按順序找這三個檔案,一旦找到,就開始讀取這個檔案並執行。

當前,我們也可以給make命令指定一個特殊名字的Makefile。要達到這個功能,我們要使用make的「-f」或是「--file」參數(「--makefile」參數也行)。例如,我們有個makefile的名字是「hchen.mk」,那麼,我們可以這樣來讓make來執行這個檔案:

make –f hchen.mk

如果在make的命令行是,你不只一次地使用了「-f」參數,那麼,所有指定的makefile將會被連在一起傳遞給make執行。

三、指定目標

一般來說,make的最終目標是makefile中的第一個目標,而其它目標一般是由這個目標連帶出來的。這是make的預設行為。當然,一般來說,你的makefile中的第一個目標是由許多個目標組成,你可以指示make,讓其完成你所指定的目標。要達到這一目的很簡單,需在make命令後直接跟目標的名字就可以完成(如前面提到的「make clean」形式)

任何在makefile中的目標都可以被指定成終極目標,但是除了以「-」打頭,或是包含了「=」的目標,因為有這些字符的目標,會被解析成命令行參數或是變量。甚至沒有被我們明確寫出來的目標也可以成為make的終極目標,也就是說,只要 make可以找到其隱含規則推導規則,那麼這個隱含目標同樣可以被指定成終極目標。

有一個make的環境變量叫「MAKECMDGOALS」,這個變量中會存放你所指定的終極目標的列表,如果在命令行上,你沒有指定目標,那麼,這個變量是空值。這個變量可以讓你使用在一些比較特殊的情形下。比如下面的例子:

sources = foo.c bar.c

ifneq ( $(MAKECMDGOALS),clean)

include $(sources:.c=.d)

endif

基於上面的這個例子,只要我們輸入的命令不是「make clean」,那麼makefile會自動包含「foo.d」和「bar.d」這兩個makefile。

使用指定終極目標的方法可以很方便地讓我們編譯我們的程序,例如下面這個例子:

.PHONY: all

all: prog1 prog2 prog3 prog4

從這個例子中,我們可以看到,這個makefile中有四個需要編譯的程序—— 「prog1」, 「prog2」, 「prog3」和 「prog4」,我們可以使用「make all」命令來編譯所有的目標(如果把all置成第一個目標,那麼只需執行「make」),我們也可以使用「make prog2」來單獨編譯目標「prog2」。

即然make可以指定所有makefile中的目標,那麼也包括「偽目標」,於是我們可以根據這種性質來讓我們的makefile根據指定的不同的目標來完成不同的事。在Unix世界中,軟體發布時,特別是GNU這種開源軟體的發布時,其 makefile都包含了編譯、安裝、打包等功能。我們可以參照這種規則來書寫我們的makefile中的目標。

「all」

這個偽目標是所有目標的目標,其功能一般是編譯所有的目標。

「clean」

這個偽目標功能是刪除所有被make建立的檔案。

「install」

這個偽目標功能是安裝已編譯好的程序,其實就是把目標執行檔案拷貝到指定的目標中去。

「print」

這個偽目標的功能是例出改變過的原始碼檔案。

「tar」

這個偽目標功能是把源程序打包備份。也就是一個tar檔案。

「dist」

這個偽目標功能是建立一個壓縮檔案,一般是把tar檔案壓成Z檔案。或是gz檔案。

「TAGS」

這個偽目標功能是更新所有的目標,以備完整地重編譯使用。

「check」和「test」

這兩個偽目標一般用來測試makefile的流程。

當然一個項目的makefile中也不一定要書寫這樣的目標,這些東西都是GNU的東西,但是我想,GNU搞出這些東西一定有其可取之處(等你的UNIX下的程序檔案一多時你就會發現這些功能很有用了),這裡只不過是說明了,如果你要書寫這種功能,最好使用這種名字命名你的目標,這樣規範一些,規範的好處就是——不用解釋,大家都明白。而且如果你的makefile中有這些功能,一是很實用,二是可以顯得你的makefile很專業(不是那種初學者的作品)。

四、檢查規則

有時候,我們不想讓我們的makefile中的規則執行起來,我們只想檢查一下我們的命令,或是執行的序列。於是我們可以使用make命令的下述參數:

「-n」

「--just-print」

「--dry-run」

「--recon」

不執行參數,這些參數隻是打印命令,不管目標是否更新,把規則和連帶規則下的命令打印出來,但不執行,這些參數對於我們調試makefile很有用處。

「-t」

「--touch」

這個參數的意思就是把目標檔案的時間更新,但不更改目標檔案。也就是說,make假裝編譯目標,但不是真正的編譯目標,只是把目標變成已編譯過的狀態。

「-q」

「--question」

這個參數的行為是找目標的意思,也就是說,如果目標存在,那麼其什麼也不會輸出,當然也不會執行編譯,如果目標不存在,其會打印出一條出錯訊息。

「-W <file>」

「--what-if=<file>」

「--assume-new=<file>」

「--new-file=<file>」

這個參數需要指定一個檔案。一般是是原始碼檔案(或相依性檔案),Make會根據規則推導來運行依賴於這個檔案的命令,一般來說,可以和「-n」參數一同使用,來查看這個相依性檔案所發生的規則命令。

另外一個很有意思的用法是結合「-p」和「-v」來輸出makefile被執行時的訊息(這個將在後面講述)。

五、make的參數

下面列舉了所有GNU make 3.80版的參數定義。其它版本和產商的make大同小異,不過其它產商的make的具體參數還是請參考各自的產品文檔。

「-b」

「-m」

這兩個參數的作用是忽略和其它版本make的兼容性。

「-B」

「--always-make」

認為所有的目標都需要更新(重編譯)。

「-C <dir>」

「--directory=<dir>」

指定讀取makefile的目錄。如果有多個「-C」參數,make的解釋是後面的路徑以前面的作為相對路徑,並以最後的目錄作為被指定目錄。如:「make –C ~hchen/test –C prog」等價於「make –C ~hchen/test/prog」。

「—debug[=<options>]」

輸出make的調試訊息。它有幾種不同的級別可供選擇,如果沒有參數,那就是輸出最簡單的調試訊息。下面是<options>的取值:

a —— 也就是all,輸出所有的調試訊息。(會非常的多)

b —— 也就是basic,只輸出簡單的調試訊息。即輸出不需要重編譯的目標。

v —— 也就是verbose,在b選項的級別之上。輸出的訊息包括哪個makefile被解析,不需要被重編譯的相依性檔案(或是依賴目標)等。

i —— 也就是implicit,輸出所以的隱含規則。

j —— 也就是jobs,輸出執行規則中命令的詳細訊息,如命令的PID、返回碼等。

m —— 也就是makefile,輸出make讀取makefile,更新makefile,執行makefile的訊息。

「-d」

相當於「--debug=a」。

「-e」

「--environment-overrides」

指明環境變量的值覆蓋makefile中定義的變量的值。

「-f=<file>」

「--file=<file>」

「--makefile=<file>」

指定需要執行的makefile。

「-h」

「--help」

顯示幫助訊息。

「-i」

「--ignore-errors」

在執行時忽略所有的錯誤。

「-I <dir>」

「--include-dir=<dir>」

指定一個被包含makefile的搜索目標。可以使用多個「-I」參數來指定多個目錄。

「-j [<jobsnum>]」

「--jobs[=<jobsnum>]」

指同時運行命令的個數。如果沒有這個參數,make運行命令時能運行多少就運行多少。如果有一個以上的「-j」參數,那麼僅最後一個「-j」才是有效的。(注意這個參數在MS-DOS中是無用的)

「-k」

「--keep-going」

出錯也不停止運行。如果生成一個目標失敗了,那麼依賴於其上的目標就不會被執行了。

「-l <load>」

「--load-average[=<load]」

「—max-load[=<load>]」

指定make運行命令的負載。

「-n」

「--just-print」

「--dry-run」

「--recon」

僅輸出執行過程中的命令序列,但並不執行。

「-o <file>」

「--old-file=<file>」

「--assume-old=<file>」

不重新生成的指定的<file>,即使這個目標的相依性檔案新於它。

「-p」

「--print-data-base」

輸出makefile中的所有數據,包括所有的規則和變量。這個參數會讓一個簡單的makefile都會輸出一堆訊息。如果你只是想輸出訊息而不想執行makefile,你可以使用「make -qp」命令。如果你想查看執行makefile前的預設變量和規則,你可以使用「make –p –f /dev/null」。這個參數輸出的訊息會包含著你的makefile檔案的檔案名和行號,所以,用這個參數來調試你的makefile會是很有用的,特別是當你的環境變量很複雜的時候。

「-q」

「--question」

不運行命令,也不輸出。僅僅是檢查所指定的目標是否需要更新。如果是0則說明要更新,如果是2則說明有錯誤發生。

「-r」

「--no-builtin-rules」

禁止make使用任何隱含規則。

「-R」

「--no-builtin-variabes」

禁止make使用任何作用於變量上的隱含規則。

「-s」

「--silent」

「--quiet」

在命令運行時不輸出命令的輸出。

「-S」

「--no-keep-going」

「--stop」

取消「-k」選項的作用。因為有些時候,make的選項是從環境變量「MAKEFLAGS」中繼承下來的。所以你可以在命令行中使用這個參數來讓環境變量中的「-k」選項失效。

「-t」

「--touch」

相當於UNIX的touch命令,只是把目標的修改日期變成最新的,也就是阻止生成目標的命令運行。

「-v」

「--version」

輸出make程序的版本、版權等關於make的訊息。

「-w」

「--print-directory」

輸出運行makefile之前和之後的訊息。這個參數對於跟蹤巢狀式呼叫make時很有用。

「--no-print-directory」

禁止「-w」選項。

「-W <file>」

「--what-if=<file>」

「--new-file=<file>」

「--assume-file=<file>」

假定目標<file>需要更新,如果和「-n」選項使用,那麼這個參數會輸出該目標更新時的運行動作。如果沒有「-n」那麼就像運行UNIX的「touch」命令一樣,使得<file>的修改時間為當前時間。

「--warn-undefined-variables」

只要make發現有未定義的變量,那麼就輸出警告訊息。

隱含規則

————

在我們使用Makefile時,有一些我們會經常使用,而且使用頻率非常高的東西,比如,我們編譯C/C++的源程序為中間目標檔案(Unix下是[.o]檔案,Windows下是[.obj]檔案)。本章講述的就是一些在Makefile中的「隱含的」,早先約定了的,不需要我們再寫出來的規則。

「隱含規則」也就是一種慣例,make會按照這種「慣例」心照不喧地來運行,那怕我們的Makefile中沒有書寫這樣的規則。例如,把[.c]檔案編譯成[.o]檔案這一規則,你根本就不用寫出來,make會自動推導出這種規則,並生成我們需要的[.o]檔案。

「隱含規則」會使用一些我們系統變量,我們可以改變這些系統變量的值來定製隱含規則的運行時的參數。如系統變量「CFLAGS」可以控制編譯時的編譯器參數。

我們還可以通過「模式規則」的方式寫下自己的隱含規則。用「後綴規則」來定義隱含規則會有許多的限制。使用「模式規則」會更回得智能和清楚,但「後綴規則」可以用來保證我們Makefile的兼容性。

我們了解了「隱含規則」,可以讓其為我們更好的服務,也會讓我們知道一些「約定俗成」了的東西,而不至於使得我們在運行Makefile時出現一些我們覺得莫名其妙的東西。當然,任何事物都是矛盾的,水能載舟,亦可覆舟,所以,有時候「隱含規則」也會給我們造成不小的麻煩。只有了解了它,我們才能更好地使用它。

一、使用隱含規則

如果要使用隱含規則生成你需要的目標,你所需要做的就是不要寫出這個目標的規則。那麼,make會試圖去自動推導產生這個目標的規則和命令,如果make可以自動推導生成這個目標的規則和命令,那麼這個行為就是隱含規則的自動推導。當然,隱含規則是make事先約定好的一些東西。例如,我們有下面的一個 Makefile:

foo : foo.o bar.o

cc –o foo foo.o bar.o $(CFLAGS) $(LDFLAGS)

我們可以注意到,這個Makefile中並沒有寫下如何生成foo.o和bar.o這兩目標的規則和命令。因為make的「隱含規則」功能會自動為我們自動去推導這兩個目標的依賴目標和生成命令。

make會在自己的「隱含規則」庫中尋找可以用的規則,如果找到,那麼就會使用。如果找不到,那麼就會報錯。在上面的那個例子中,make呼叫的隱含規則是,把[.o]的目標的相依性檔案置成[.c],並使用C的編譯命令「cc –c $(CFLAGS) [.c]」來生成[.o]的目標。也就是說,我們完全沒有必要寫下下面的兩條規則:

foo.o : foo.c

cc –c foo.c $(CFLAGS)

bar.o : bar.c

cc –c bar.c $(CFLAGS)

因為,這已經是「約定」好了的事了,make和我們約定好了用C編譯器「cc」生成[.o]檔案的規則,這就是隱含規則。

當然,如果我們為[.o]檔案書寫了自己的規則,那麼make就不會自動推導並呼叫隱含規則,它會按照我們寫好的規則忠實地執行。

還有,在make的「隱含規則庫」中,每一條隱含規則都在庫中有其順序,越靠前的則是越被經常使用的,所以,這會導致我們有些時候即使我們顯示地指定了目標依賴,make也不會管。如下面這條規則(沒有命令):

foo.o : foo.p

相依性檔案「foo.p」(Pascal程序的原始碼檔案)有可能變得沒有意義。如果目錄下存在了「foo.c」檔案,那麼我們的隱含規則一樣會生效,並會通過「foo.c」呼叫C的編譯器生成foo.o檔案。因為,在隱含規則中,Pascal的規則出現在C的規則之後,所以,make找到可以生成foo.o的C的規則就不再尋找下一條規則了。如果你確實不希望任何隱含規則推導,那麼,你就不要只寫出「依賴規則」,而不寫命令。

二、隱含規則一覽

這裡我們將講述所有預先設置(也就是make內建)的隱含規則,如果我們不明確地寫下規則,那麼,make就會在這些規則中尋找所需要規則和命令。當然,我們也可以使用make的參數「-r」或「--no-builtin-rules」選項來取消所有的預設置的隱含規則。

當然,即使是我們指定了「-r」參數,某些隱含規則還是會生效,因為有許多的隱含規則都是使用了「後綴規則」來定義的,所以,只要隱含規則中有「後綴列表」(也就一系統定義在目標.SUFFIXES的依賴目標),那麼隱含規則就會生效。預設的後綴列表是:.out, .a, .ln, .o, .c, .cc, .C, .p, .f, .F, .r, .y, .l, .s, .S, .mod, .sym, .def, .h, .info, .dvi, .tex, .texinfo, .texi, .txinfo, .w, .ch .web, .sh, .elc, .el。具體的細節,我們會在後面講述。

還是先來看一看常用的隱含規則吧。

1、編譯C程序的隱含規則。

「<n>.o」的目標的依賴目標會自動推導為「<n>.c」,並且其生成命令是「$(CC) –c $(CPPFLAGS) $(CFLAGS)」

2、編譯C++程序的隱含規則。

「<n>. o」的目標的依賴目標會自動推導為「<n>.cc」或是「<n>.C」,並且其生成命令是「$(CXX) –c $(CPPFLAGS) $(CFLAGS)」。(建議使用「.cc」作為C++原始碼檔案的後綴,而不是「.C」)

3、編譯Pascal程序的隱含規則。

「<n>.o」的目標的依賴目標會自動推導為「<n>.p」,並且其生成命令是「$(PC) –c $(PFLAGS)」。

4、編譯Fortran/Ratfor程序的隱含規則。

「<n>.o」的目標的依賴目標會自動推導為「<n>.r」或「<n>.F」或「<n>.f」,並且其生成命令是:

「.f」 「$(FC) –c $(FFLAGS)」

「.F」 「$(FC) –c $(FFLAGS) $(CPPFLAGS)」

「.f」 「$(FC) –c $(FFLAGS) $(RFLAGS)」

5、預處理Fortran/Ratfor程序的隱含規則。

「<n>.f」的目標的依賴目標會自動推導為「<n>.r」或「<n>.F」。這個規則只是轉換Ratfor或有預處理的Fortran程序到一個標準的Fortran程序。其使用的命令是:

「.F」 「$(FC) –F $(CPPFLAGS) $(FFLAGS)」

「.r」 「$(FC) –F $(FFLAGS) $(RFLAGS)」

6、編譯Modula-2程序的隱含規則。

「< n>.sym」的目標的依賴目標會自動推導為「<n>.def」,並且其生成命令是:「$(M2C) $(M2FLAGS) $(DEFFLAGS)」。「<n.o>」的目標的依賴目標會自動推導為「<n>.mod」,並且其生成命令是:「$(M2C) $(M2FLAGS) $(MODFLAGS)」。

7、組合和組合預處理的隱含規則。

「<n>. o」 的目標的依賴目標會自動推導為「<n>.s」,預設使用編譯品「as」,並且其生成命令是:「$(AS) $(ASFLAGS)」。「<n>.s」的目標的依賴目標會自動推導為「<n>.S」,預設使用C預編譯器「cpp」,並且其生成命令是:「$(AS) $(ASFLAGS)」。

8、連結Object檔案的隱含規則。

「<n>」目標依賴於「<n>.o」,通過運行C的編譯器來運行連結程式生成(一般是「ld」),其生成命令是:「$(CC) $(LDFLAGS) <n>.o $(LOADLIBES) $(LDLIBS)」。這個規則對於只有一個原始碼檔案的專案有效,同時也對多個Object檔案(由不同的原始碼檔案生成)的也有效。例如如下規則:

x : y.o z.o

並且「x.c」、「y.c」和「z.c」都存在時,隱含規則將執行如下命令:

cc -c x.c -o x.o

cc -c y.c -o y.o

cc -c z.c -o z.o

cc x.o y.o z.o -o x

rm -f x.o

rm -f y.o

rm -f z.o

如果沒有一個原始碼檔案(如上例中的x.c)和你的目標名字(如上例中的x)相關聯,那麼,你最好寫出自己的生成規則,不然,隱含規則會報錯的。

9、Yacc C程序時的隱含規則。

「<n>.c」的相依性檔案被自動推導為「n.y」(Yacc生成的檔案),其生成命令是:「$(YACC) $(YFALGS)」。(「Yacc」是一個語法分析器,關於其細節請查看相關資料)

10、Lex C程序時的隱含規則。

「<n>.c」的相依性檔案被自動推導為「n.l」(Lex生成的檔案),其生成命令是:「$(LEX) $(LFALGS)」。(關於「Lex」的細節請查看相關資料)

11、Lex Ratfor程序時的隱含規則。

「<n>.r」的相依性檔案被自動推導為「n.l」(Lex生成的檔案),其生成命令是:「$(LEX) $(LFALGS)」。

12、從C程序、Yacc檔案或Lex檔案建立Lint庫的隱含規則。

「<n>.ln」 (lint生成的檔案)的相依性檔案被自動推導為「n.c」,其生成命令是:「$(LINT) $(LINTFALGS) $(CPPFLAGS) -i」。對於「<n>.y」和「<n>.l」也是同樣的規則。

三、隱含規則使用的變量

在隱含規則中的命令中,基本上都是使用了一些預先設置的變量。你可以在你的makefile中改變這些變量的值,或是在make的命令行中傳入這些值,或是在你的環境變量中設置這些值,無論怎麼樣,只要設置了這些特定的變量,那麼其就會對隱含規則起作用。當然,你也可以利用make的「-R」或「--no–builtin -variables」參數來取消你所定義的變量對隱含規則的作用。

例如,第一條隱含規則——編譯C程序的隱含規則的命令是「$(CC) –c $(CFLAGS) $(CPPFLAGS)」。Make預設的編譯命令是「cc」,如果你把變量「$(CC)」重定義成「gcc」,把變量「$(CFLAGS)」重定義成「-g」,那麼,隱含規則中的命令全部會以「gcc –c -g $(CPPFLAGS)」的樣子來執行了。

我們可以把隱含規則中使用的變量分成兩種:一種是命令相關的,如「CC」;一種是參數相的關,如「CFLAGS」。下面是所有隱含規則中會用到的變量:

1、關於命令的變量。

AR

函數庫打包程序。預設命令是「ar」。

AS

組合語言編譯程序。預設命令是「as」。

CC

C語言編譯程序。預設命令是「cc」。

CXX

C++語言編譯程序。預設命令是「g++」。

CO

從 RCS檔案中擴展檔案程序。預設命令是「co」。

CPP

C程序的預處理器(輸出是標準輸出設備)。預設命令是「$(CC) –E」。

FC

Fortran 和 Ratfor 的編譯器和預處理程序。預設命令是「f77」。

GET

從SCCS檔案中擴展檔案的程序。預設命令是「get」。

LEX

Lex方法分析器程序(針對於C或Ratfor)。預設命令是「lex」。

PC

Pascal語言編譯程序。預設命令是「pc」。

YACC

Yacc文法分析器(針對於C程序)。預設命令是「yacc」。

YACCR

Yacc文法分析器(針對於Ratfor程序)。預設命令是「yacc –r」。

MAKEINFO

轉換Texinfo原始碼檔案(.texi)到Info檔案程序。預設命令是「makeinfo」。

TEX

從TeX原始碼檔案建立TeX DVI檔案的程序。預設命令是「tex」。

TEXI2DVI

從Texinfo原始碼檔案建立TeX DVI 檔案的程序。預設命令是「texi2dvi」。

WEAVE

轉換Web到TeX的程序。預設命令是「weave」。

CWEAVE

轉換C Web 到 TeX的程序。預設命令是「cweave」。

TANGLE

轉換Web到Pascal語言的程序。預設命令是「tangle」。

CTANGLE

轉換C Web 到 C。預設命令是「ctangle」。

RM

刪除檔案命令。預設命令是「rm –f」。

2、關於命令參數的變量

下面的這些變量都是相關上面的命令的參數。如果沒有指明其預設值,那麼其預設值都是空。

ARFLAGS

函數庫打包程序AR命令的參數。預設值是「rv」。

ASFLAGS

組合語言編譯器參數。(當明顯地呼叫「.s」或「.S」檔案時)。

CFLAGS

C語言編譯器參數。

CXXFLAGS

C++語言編譯器參數。

COFLAGS

RCS命令參數。

CPPFLAGS

C預處理器參數。( C 和 Fortran 編譯器也會用到)。

FFLAGS

Fortran語言編譯器參數。

GFLAGS

SCCS 「get」程序參數。

LDFLAGS

連結器參數。(如:「ld」)

LFLAGS

Lex文法分析器參數。

PFLAGS

Pascal語言編譯器參數。

RFLAGS

Ratfor 程序的Fortran 編譯器參數。

YFLAGS

Yacc文法分析器參數。

四、隱含規則鏈

有些時候,一個目標可能被一系列的隱含規則所作用。例如,一個[.o]的檔案生成,可能會是先被Yacc的[.y]檔案先成[.c],然後再被C的編譯器生成。我們把這一系列的隱含規則叫做「隱含規則鏈」。

在上面的例子中,如果檔案[.c]存在,那麼就直接呼叫C的編譯器的隱含規則,如果沒有[.c]檔案,但有一個[.y]檔案,那麼Yacc的隱含規則會被呼叫,生成[.c]檔案,然後,再呼叫C編譯的隱含規則最終由[.c]生成[.o]檔案,達到目標。

我們把這種[.c]的檔案(或是目標),叫做中間目標。不管怎麼樣,make會努力自動推導生成目標的一切方法,不管中間目標有多少,其都會執著地把所有的隱含規則和你書寫的規則全部合起來分析,努力達到目標,所以,有些時候,可能會讓你覺得奇怪,怎麼我的目標會這樣生成?怎麼我的makefile發瘋了?

在預設情況下,對於中間目標,它和一般的目標有兩個地方所不同:第一個不同是除非中間的目標不存在,才會引發中間規則。第二個不同的是,只要目標成功產生,那麼,產生最終目標過程中,所產生的中間目標檔案會被以「rm -f」刪除。

通常,一個被makefile指定成目標或是依賴目標的檔案不能被當作中介。然而,你可以明顯地說明一個檔案或是目標是中介目標,你可以使用偽目標「.INTERMEDIATE」來強制宣告。(如:.INTERMEDIATE : mid )

你也可以阻止make自動刪除中間目標,要做到這一點,你可以使用偽目標「.SECONDARY」來強制宣告(如:.SECONDARY : sec)。你還可以把你的目標,以模式的方式來指定(如:%.o)成偽目標「.PRECIOUS」的依賴目標,以保存被隱含規則所生成的中間檔案。

在「隱含規則鏈」中,禁止同一個目標出現兩次或兩次以上,這樣一來,就可防止在make自動推導時出現無限遞歸的情況。

Make會優化一些特殊的隱含規則,而不生成中間檔案。如,從檔案「foo.c」生成目標程序「foo」,按道理,make會編譯生成中間檔案「foo.o」,然後連結成「foo」,但在實際情況下,這一動作可以被一條「cc」的命令完成(cc –o foo foo.c),於是優化過的規則就不會生成中間檔案。

五、定義模式規則

你可以使用模式規則來定義一個隱含規則。一個模式規則就好像一個一般的規則,只是在規則中,目標的定義需要有"%"字符。"%"的意思是表示一個或多個任意字符。在依賴目標中同樣可以使用"%",只是依賴目標中的"%"的取值,取決於其目標。

有一點需要注意的是,"%"的展開發生在變量和函數的展開之後,變量和函數的展開發生在make載入Makefile時,而模式規則中的"%"則發生在運行時。

1、模式規則介紹

模式規則中,至少在規則的目標定義中要包含"%",否則,就是一般的規則。目標中的"%"定義表示對檔案名的匹配,"%"表示長度任意的非空字串。例如:"%.c"表示以".c"結尾的檔案名(檔案名的長度至少為3),而"s.%.c"則表示以 "s."開頭,".c"結尾的檔案名(檔案名的長度至少為5)。

如果"%"定義在目標中,那麼,目標中的"%"的值決定了依賴目標中的"%"的值,也就是說,目標中的模式的"%"決定了依賴目標中"%"的樣子。例如有一個模式規則如下:

%.o : %.c ; <command ......>

其含義是,指出了怎麼從所有的[.c]檔案生成相應的[.o]檔案的規則。如果要生成的目標是"a.o b.o",那麼"%c"就是"a.c b.c"。

一旦依賴目標中的"%"模式被確定,那麼,make會被要求去匹配當前目錄下所有的檔案名,一旦找到,make就會規則下的命令,所以,在模式規則中,目標可能會是多個的,如果有模式匹配出多個目標,make就會產生所有的模式目標,此時, make關心的是依賴的檔案名和生成目標的命令這兩件事。

2、模式規則範例

下面這個例子表示了,把所有的[.c]檔案都編譯成[.o]檔案.

%.o : %.c

$(CC) -c $(CFLAGS) $(CPPFLAGS) $< -o $@

其中,"$@"表示所有的目標的挨個值,"$<"表示了所有依賴目標的挨個值。這些奇怪的變量我們叫"自動化變量",後面會詳細講述。

下面的這個例子中有兩個目標是模式的:

%.tab.c %.tab.h: %.y

bison -d $<

這條規則告訴make把所有的[.y]檔案都以"bison -d <n>.y"執行,然後生成"<n>.tab.c"和"<n>.tab.h"檔案。(其中,"<n>" 表示一個任意字串)。如果我們的執行程序"foo"依賴於檔案"parse.tab.o"和"scan.o",並且檔案"scan.o"依賴於檔案 "parse.tab.h",如果"parse.y"檔案被更新了,那麼根據上述的規則,"bison -d parse.y"就會被執行一次,於是,"parse.tab.o"和"scan.o"的相依性檔案就齊了。(假設,"parse.tab.o"由 "parse.tab.c"生成,和"scan.o"由"scan.c"生成,而"foo"由"parse.tab.o"和"scan.o"連結生成,而且foo和其[.o]檔案的依賴關係也寫好,那麼,所有的目標都會得到滿足)

3、自動化變量

在上述的模式規則中,目標和相依性檔案都是一系例的檔案,那麼我們如何書寫一個命令來完成從不同的相依性檔案生成相應的目標?因為在每一次的對模式規則的解析時,都會是不同的目標和相依性檔案。

自動化變量就是完成這個功能的。在前面,我們已經對自動化變量有所提涉,相信你看到這裡已對它有一個感性認識了。所謂自動化變量,就是這種變量會把模式中所定義的一系列的檔案自動地挨個取出,直至所有的符合模式的檔案都取完了。這種自動化變量只應出現在規則的命令中。

下面是所有的自動化變量及其說明:

$@

表示規則中的目標檔案集。在模式規則中,如果有多個目標,那麼,"$@"就是匹配於目標中模式定義的集合。

$%

僅當目標是函數函式庫檔案中,表示規則中的目標成員名。例如,如果一個目標是"foo.a(bar.o)",那麼,"$%"就是"bar.o","$@"就是 "foo.a"。如果目標不是函數函式庫檔案(Unix下是[.a],Windows下是[.lib]),那麼,其值為空。

$<

依賴目標中的第一個目標名字。如果依賴目標是以模式(即"%")定義的,那麼"$<"將是符合模式的一系列的檔案集。注意,其是一個一個取出來的。

$?

所有比目標新的依賴目標的集合。以空格分隔。

$^

所有的依賴目標的集合。以空格分隔。如果在依賴目標中有多個重複的,那個這個變量會去除重複的依賴目標,只保留一份。

$+

這個變量很像"$^",也是所有依賴目標的集合。只是它不去除重複的依賴目標。

$*

這個變量表示目標模式中"%"及其之前的部分。如果目標是"dir/a.foo.b",並且目標的模式是"a.%.b",那麼,"$*"的值就是 "dir/a.foo"。這個變量對於構造有關聯的檔案名是比較有較。如果目標中沒有模式的定義,那麼"$*"也就不能被推導出,但是,如果目標檔案的後綴是make所識別的,那麼"$*"就是除了後綴的那一部分。例如:如果目標是"foo.c",因為".c"是make所能識別的後綴名,所以,"$*" 的值就是"foo"。這個特性是GNU make的,很有可能不兼容於其它版本的make,所以,你應該儘量避免使用"$*",除非是在隱含規則或是靜態模式中。如果目標中的後綴是make所不能識別的,那麼"$*"就是空值。

當你希望只對更新過的相依性檔案進行操作時,"$?"在顯式規則中很有用,例如,假設有一個函數函式庫檔案叫"lib",其由其它幾個object檔案更新。那麼把object檔案打包的比較有效率的Makefile規則是:

lib : foo.o bar.o lose.o win.o

ar r lib $?

在上述所列出來的自動量變量中。四個變量($@、$<、$%、$*)在擴展時只會有一個檔案,而另三個的值是一個檔案列表。這七個自動化變量還可以取得檔案的目錄名或是在當前目錄下的符合模式的檔案名,只需要搭配上"D"或"F"字樣。這是 GNU make中老版本的特性,在新版本中,我們使用函數"dir"或"notdir"就可以做到了。"D"的含義就是Directory,就是目錄,"F"的含義就是File,就是檔案。

下面是對於上面的七個變量分別加上"D"或是"F"的含義:

$(@D)

表示"$@"的目錄部分(不以斜槓作為結尾),如果"$@"值是"dir/foo.o",那麼"$(@D)"就是"dir",而如果"$@"中沒有包含斜槓的話,其值就是"."(當前目錄)。

$(@F)

表示"$@"的檔案部分,如果"$@"值是"dir/foo.o",那麼"$(@F)"就是"foo.o","$(@F)"相當於函數"$(notdir $@)"。

"$(*D)"

"$(*F)"

和上面所述的同理,也是取檔案的目錄部分和檔案部分。對於上面的那個例子,"$(*D)"返回"dir",而"$(*F)"返回"foo"

"$(%D)"

"$(%F)"

分別表示了函數包檔案成員的目錄部分和檔案部分。這對於形同"archive(member)"形式的目標中的"member"中包含了不同的目錄很有用。

"$(<D)"

"$(<F)"

分別表示相依性檔案的目錄部分和檔案部分。

"$(^D)"

"$(^F)"

分別表示所有相依性檔案的目錄部分和檔案部分。(無相同的)

"$(+D)"

"$(+F)"

分別表示所有相依性檔案的目錄部分和檔案部分。(可以有相同的)

"$(?D)"

"$(?F)"

分別表示被更新的相依性檔案的目錄部分和檔案部分。

最後想提醒一下的是,對於"$<",為了避免產生不必要的麻煩,我們最好給$後面的那個特定字符都加上圓括號,比如,"$(<)"就要比"$<"要好一些。

還得要注意的是,這些變量只使用在規則的命令中,而且一般都是"顯式規則"和"靜態模式規則"(參見前面"書寫規則"一章)。其在隱含規則中並沒有意義。

4、模式的匹配

一般來說,一個目標的模式有一個有前綴或是後綴的"%",或是沒有前後綴,直接就是一個"% "。因為"%"代表一個或多個字符,所以在定義好了的模式中,我們把"%"所匹配的內容叫做"莖",例如"%.c"所匹配的檔案"test.c"中 "test"就是"莖"。因為在目標和依賴目標中同時有"%"時,依賴目標的"莖"會傳給目標,當做目標中的"莖"。

當一個模式匹配包含有斜槓(實際也不經常包含)的檔案時,那麼在進行模式匹配時,目錄部分會首先被移開,然後進行匹配,成功後,再把目錄加回去。在進行"莖"的傳遞時,我們需要知道這個步驟。例如有一個模式"e%t",檔案"src/eat"匹配於該模式,於是"src/a"就是其"莖",如果這個模式定義在依賴目標中,而被依賴於這個模式的目標中又有個模式"c%r",那麼,目標就是 "src/car"。("莖"被傳遞)

5、重載內建隱含規則

你可以重載內建的隱含規則(或是定義一個全新的),例如你可以重新構造和內建隱含規則不同的命令,如:

%.o : %.c

$(CC) -c $(CPPFLAGS) $(CFLAGS) -D$(date)

你可以取消內建的隱含規則,只要不在後面寫命令就行。如:

%.o : %.s

同樣,你也可以重新定義一個全新的隱含規則,其在隱含規則中的位置取決於你在哪裡寫下這個規則。朝前的位置就靠前。

六、老式風格的"後綴規則"

後綴規則是一個比較老式的定義隱含規則的方法。後綴規則會被模式規則逐步地取代。因為模式規則更強更清晰。為了和老版本的Makefile兼容,GNU make同樣兼容於這些東西。後綴規則有兩種方式:"雙後綴"和"單後綴"。

雙後綴規則定義了一對後綴:目標檔案的後綴和依賴目標(原始碼檔案)的後綴。如".c.o"相當於"%o : %c"。單後綴規則只定義一個後綴,也就是原始碼檔案的後綴。如".c"相當於"% : %.c"。

後綴規則中所定義的後綴應該是make所認識的,如果一個後綴是make所認識的,那麼這個規則就是單後綴規則,而如果兩個連在一起的後綴都被make所認識,那就是雙後綴規則。例如:".c"和".o"都是make所知道。因而,如果你定義了一個規則是".c.o"那麼其就是雙後綴規則,意義就是".c"是原始碼檔案的後綴,".o"是目標檔案的後綴。如下範例:

.c.o:

$(CC) -c $(CFLAGS) $(CPPFLAGS) -o $@ $<

後綴規則不允許任何的相依性檔案,如果有相依性檔案的話,那就不是後綴規則,那些後綴統統被認為是檔案名,如:

.c.o: foo.h

$(CC) -c $(CFLAGS) $(CPPFLAGS) -o $@ $<

這個例子,就是說,檔案".c.o"依賴於檔案"foo.h",而不是我們想要的這樣:

%.o: %.c foo.h

$(CC) -c $(CFLAGS) $(CPPFLAGS) -o $@ $<

後綴規則中,如果沒有命令,那是毫無意義的。因為他也不會移去內建的隱含規則。

而要讓make知道一些特定的後綴,我們可以使用偽目標".SUFFIXES"來定義或是刪除,如:

.SUFFIXES: .hack .win

把後綴.hack和.win加入後綴列表中的末尾。

.SUFFIXES: # 刪除預設的後綴

.SUFFIXES: .c .o .h # 定義自己的後綴

先清楚預設後綴,後定義自己的後綴列表。

make的參數"-r"或"-no-builtin-rules"也會使用得預設的後綴列表為空。而變量"SUFFIXE"被用來定義預設的後綴列表,你可以用".SUFFIXES"來改變後綴列表,但請不要改變變量"SUFFIXE"的值。

七、隱含規則搜索算法

比如我們有一個目標叫 T。下面是搜索目標T的規則的算法。請注意,在下面,我們沒有提到後綴規則,原因是,所有的後綴規則在Makefile被載入內存時,會被轉換成模式規則。如果目標是"archive(member)"的函數函式庫檔案模式,那麼這個算法會被運行兩次,第一次是找目標T,如果沒有找到的話,那麼進入第二次,第二次會把"member"當作T來搜索。

1、把T的目錄部分分離出來。叫D,而剩餘部分叫N。(如:如果T是"src/foo.o",那麼,D就是"src/",N就是"foo.o")

2、建立所有匹配於T或是N的模式規則列表。

3、如果在模式規則列表中有匹配所有檔案的模式,如"%",那麼從列表中移除其它的模式。

4、移除列表中沒有命令的規則。

5、對於第一個在列表中的模式規則:

1)推導其"莖"S,S應該是T或是N匹配於模式中"%"非空的部分。

2)計算相依性檔案。把相依性檔案中的"%"都替換成"莖"S。如果目標模式中沒有包含斜框字符,而把D加在第一個相依性檔案的開頭。

3)測試是否所有的相依性檔案都存在或是理當存在。(如果有一個檔案被定義成另外一個規則的目標檔案,或者是一個顯式規則的相依性檔案,那麼這個檔案就叫"理當存在")

4)如果所有的相依性檔案存在或是理當存在,或是就沒有相依性檔案。那麼這條規則將被採用,退出該算法。

6、如果經過第5步,沒有模式規則被找到,那麼就做更進一步的搜索。對於存在於列表中的第一個模式規則:

1)如果規則是終止規則,那就忽略它,繼續下一條模式規則。

2)計算相依性檔案。(同第5步)

3)測試所有的相依性檔案是否存在或是理當存在。

4)對於不存在的相依性檔案,遞歸呼叫這個算法查找他是否可以被隱含規則找到。

5)如果所有的相依性檔案存在或是理當存在,或是就根本沒有相依性檔案。那麼這條規則被採用,退出該算法。

7、如果沒有隱含規則可以使用,查看".DEFAULT"規則,如果有,採用,把".DEFAULT"的命令給T使用。

一旦規則被找到,就會執行其相當的命令,而此時,我們的自動化變量的值才會生成。

使用make更新函數函式庫檔案

———————————

函數函式庫檔案也就是對Object檔案(程序編譯的中間檔案)的打包檔案。在Unix下,一般是由命令"ar"來完成打包工作。

一、函數函式庫檔案的成員

一個函數函式庫檔案由多個檔案組成。你可以以如下格式指定函數函式庫檔案及其組成:

archive(member)

這個不是一個命令,而一個目標和依賴的定義。一般來說,這種用法基本上就是為了"ar"命令來服務的。如:

foolib(hack.o) : hack.o

ar cr foolib hack.o

如果要指定多個member,那就以空格分開,如:

foolib(hack.o kludge.o)

其等價於:

foolib(hack.o) foolib(kludge.o)

你還可以使用Shell的檔案通配符來定義,如:

foolib(*.o)

二、函數庫成員的隱含規則

當make搜索一個目標的隱含規則時,一個特殊的特性是,如果這個目標是"a(m)"形式的,其會把目標變成"(m)"。於是,如果我們的成員是"%.o"的模式定義,並且如果我們使用"make foo.a(bar.o)"的形式呼叫Makefile時,隱含規則會去找"bar.o"的規則,如果沒有定義bar.o的規則,那麼內建隱含規則生效, make會去找bar.c檔案來生成bar.o,如果找得到的話,make執行的命令大致如下:

cc -c bar.c -o bar.o

ar r foo.a bar.o

rm -f bar.o

還有一個變量要注意的是"$%",這是專屬函數函式庫檔案的自動化變量,有關其說明請參見"自動化變量"一節。

三、函數函式庫檔案的後綴規則

你可以使用"後綴規則"和"隱含規則"來生成函數庫打包檔案,如:

.c.a:

$(CC) $(CFLAGS) $(CPPFLAGS) -c $< -o $*.o

$(AR) r $@ $*.o

$(RM) $*.o

其等效於:

(%.o) : %.c

$(CC) $(CFLAGS) $(CPPFLAGS) -c $< -o $*.o

$(AR) r $@ $*.o

$(RM) $*.o

四、注意事項

在進行函數庫打包檔案生成時,請小心使用make的並行機制("-j"參數)。如果多個ar命令在同一時間運行在同一個函數庫打包檔案上,就很有可以損壞這個函數函式庫檔案。所以,在make未來的版本中,應該提供一種機制來避免並行操作發生在函數打包檔案上。

但就目前而言,你還是應該不要儘量不要使用"-j"參數。

後序

——

終於到寫結束語的時候了,以上基本上就是GNU make的Makefile的所有細節了。其它的產商的make基本上也就是這樣的,無論什麼樣的make,都是以檔案的依賴性為基礎的,其基本是都是遵循一個標準的。這篇文檔中80%的技術細節都適用於任何的make,我猜測"函數"那一章的內容可能不是其它make所支持的,而隱含規則方面,我想不同的make會有不同的實現,我沒有精力來查看GNU的make和VC的nmake、BCB的make,或是別的UNIX下的make有些什麼樣的差別,一是時間精力不夠,二是因為我基本上都是在Unix下使用make,以前在SCO Unix和IBM的AIX,現在在Linux、Solaris、HP-UX、AIX和Alpha下使用,Linux和Solaris下更多一點。不過,我可以肯定的是,在Unix下的make,無論是哪種平台,幾乎都使用了Richard Stallman開發的make和cc/gcc的編譯器,而且,基本上都是GNU的make(公司裡所有的UNIX機器上都被裝上了GNU的東西,所以,使用GNU的程序也就多了一些)。GNU的東西還是很不錯的,特別是使用得深了以後,越來越覺得GNU的軟體的強大,也越來越覺得GNU的在作業系統中(主要是Unix,甚至Windows)"殺傷力"。

對於上述所有的make的細節,我們不但可以利用make這個工具來編譯我們的程序,還可以利用make來完成其它的工作,因為規則中的命令可以是任何Shell之下的命令,所以,在Unix下,你不一定只是使用程序語言的編譯器,你還可以在 Makefile中書寫其它的命令,如:tar、awk、mail、sed、cvs、compress、ls、rm、yacc、rpm、ftp……等等,等等,來完成諸如"程序打包"、"程序備份"、"製作程序安裝包"、"提交程式碼"、"使用程序模板"、"合併檔案"等等五花八門的功能,檔案操作,檔案管理,編程開發設計,或是其它一些異想天開的東西。比如,以前在書寫銀行交易程序時,由於銀行的交易程序基本一樣,就見到有人書寫了一些交易的通用程序模板,在該模板中把一些網絡通訊、數據庫操作的、業務操作共性的東西寫在一個檔案中,在這些檔案中用些諸如"@@@N、###N"奇怪字串標註一些位置,然後書寫交易時,只需按照一種特定的規則書寫特定的處理,最後在make時,使用awk和sed,把模板中的"@@@N、###N"等字串替代成特定的程序,形成C檔案,然後再編譯。這個動作很像數據庫的"擴展C"語言(即在C語言中用"EXEC SQL"的樣子執行SQL語句,在用cc/gcc編譯之前,需要使用"擴展C"的翻譯程序,如cpre,把其翻譯成標準C)。如果你在使用make時有一些更為絕妙的方法,請記得告訴我啊。

回頭看看整篇文檔,不覺記起幾年前剛剛開始在Unix下做開發的時候,有人問我會不會寫 Makefile時,我兩眼發直,根本不知道在說什麼。一開始看到別人在vi中寫完程序後輸入"!make"時,還以為是vi的功能,後來才知道有一個 Makefile在作怪,於是上網查啊查,那時又不願意看英文,發現就根本沒有中文的文檔介紹Makefile,只得看別人寫的Makefile,自己瞎碰瞎搞才積累了一點知識,但在很多地方完全是知其然不知所以然。後來開始從事UNIX下產品軟體的開發,看到一個400人年,近200萬行程式碼的大專案,發現要編譯這樣一個龐然大物,如果沒有Makefile,那會是多麼恐怖的一樣事啊。於是橫下心來,狠命地讀了一堆英文文檔,才覺得對其掌握了。但發現目前網上對Makefile介紹的文章還是少得那麼的可憐,所以想寫這樣一篇文章,共享給大家,希望能對各位有所幫助。

現在我終於寫完了,看了看檔案的建立時間,這篇技術文檔也寫了兩個多月了。發現,自己知道是一回事,要寫下來,跟別人講述又是另外一回事,而且,現在越來越沒有時間專研技術細節,所以在寫作時,發現在闡述一些細節問題時很難做到嚴謹和精練,而且對先講什麼後講什麼不是很清楚,所以,還是參考了一些國外站點上的資料和題綱,以及一些技術書籍的語言風格,才得以完成。整篇文檔的提綱是基於GNU的 Makefile技術手冊的提綱來書寫的,並結合了自己的工作經驗,以及自己的學習歷程。因為從來沒有寫過這麼長,這麼細的文檔,所以一定會有很多地方存在表達問題,語言歧義或是錯誤。因些,我迫切地得等待各位給我指證和建議,以及任何的反饋。

最後,還是利用這個後序,介紹一下自己。我目前從事於所有 Unix平台下的軟體研發,主要是做分布式計算/ 網格計算方面的系統產品軟體,並且我對於下一代的計算機革命——網格計算非常地感興趣,對於分布式計算、P2P 、Web Service、 J2EE技術方向也很感興趣,同時,對於項目實施、團隊管理、項目管理也小有心得,希望同樣和我戰鬥在「技術和管理並重 」的陣線上的年輕一代,能夠和我多多地交流。我的MSN是: haoel@hotmail.com (常用), QQ是: 753640(不常用)。(註:請勿給我MSN 的郵箱發信,由於hotmail的垃圾郵件導致我拒收這個郵箱的所有來信)

我歡迎任何形式的交流,無論是討論技術還是管理,或是其它海闊天空的東西。除了政治和娛樂新聞我不關心,其它只要積極向上的東西我都歡迎!

最最後,我還想介紹一下make程序的設計開發者。

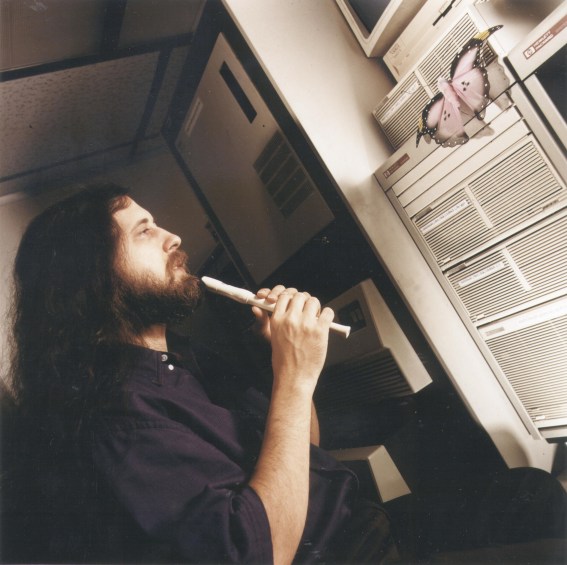

首當其衝的是:

Richard Stallman

開源軟件的領袖和先驅,從來沒有領過一天工資,從來沒有使用過

Windows操作系統。對於他的事蹟和他的軟件以及他的思想,我無需說過多的話

計算機、音樂、蝴蝶就是他的最愛

第二位是:Roland McGrath

個人主頁是: http://www.frob.com/~roland/ ,下面是他的一些事蹟:

1)

合作編寫了並維護GNU

make。

2) 和 Thomas Bushnell一同編寫了GNU Hurd 。

3) 編寫並維護著GNU C library 。

4) 合作編寫並維護著部分的GNU Emacs 。

在此,向這兩位開放原始碼的鬥士致以最真切的敬意。

留言列表

留言列表